# DS3170DK DS3/E3 Single-Chip Transceiver Design Kit

#### www.maxim-ic.com

## **GENERAL DESCRIPTION**

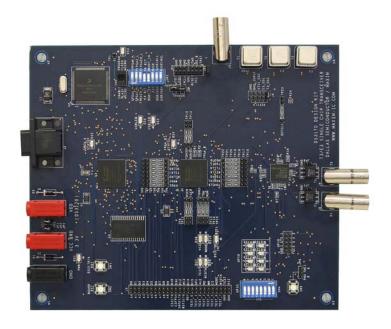

The DS3170DK is a fully integrated design kit for the DS3170 DS3/E3 single-chip transceiver (SCT). This design kit contains all the necessary circuitry to evaluate the DS3170 in all modes of operation. The design kit also includes an on-board microprocessor to run real-time code for further part evaluation.

### **DESIGN KIT CONTENTS**

DS3170DK Board Download:

ChipView Software

DS3170DK.DEF Definition File

DS3170DK Data Sheet

## ORDERING INFORMATION

| PART     | DESCRIPTION                      |

|----------|----------------------------------|

| DS3170DK | Design Kit for the DS3170 DS3/E3 |

|          | Single-Chip Transceiver          |

Windows is a registered trademark of Microsoft Corp.

#### **FEATURES**

- Expedites New Designs by Eliminating First-Pass Prototyping

- Demonstrates Key Functions of the DS3170 DS3/E3 Single-Chip Transceiver (SCT)

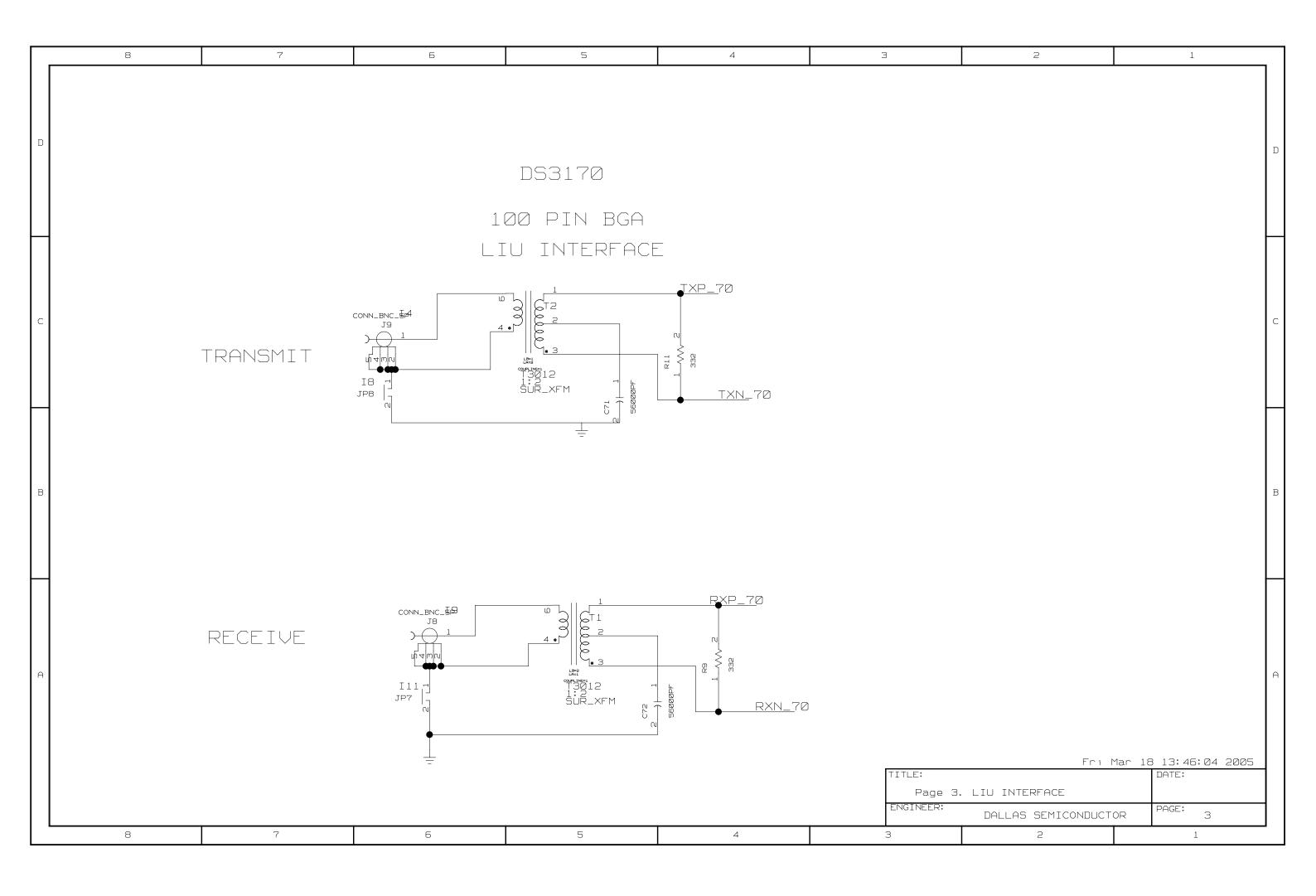

- Includes DS3170 Single-Chip Transceiver (SCT), Transformers, 75Ω BNC, and Termination Passives

- Interfaces with Any PC with an RS-232 Serial Interface

- High Level Windows®-Based Software Provides Visual Access to All Registers

- Software Controlled (Register) Mapped Configuration Switches Facilitate Real-Time Clock and Signal Routing

- Precision Test Points for All Clocks and Signals

- On-Board DS3 and E3 Crystal Oscillators for Stable Clock Generation

- Easy-to-Read Silkscreen Labels Identify the Signals Associated with All Connectors, Jumpers, and LEDS

1 of 40 REV: 091205

## **COMPONENT LIST**

| DESIGNATION                                                                                                                                                   | QTY | DESCRIPTION                                         | SUPPLIER                 | PART NUMBER     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------|--------------------------|-----------------|

| C1, C4, C5, C10,<br>C14, C15, C18,<br>C19, C21, C24,<br>C25–C32, C36-<br>C38, C39–C44,<br>C47–C49, C50,<br>C52–C56,<br>C59–C61, C66,<br>C68, C70, C73,<br>C74 | 44  | 0.1μF 20%, 16V X7R ceramic capacitors (0603)        | AVX                      | 0603YC104MAT    |

| C2, C3, C16, C17,<br>C20, C22, C23,<br>C33, C34, C51,<br>C57, C69, C75                                                                                        | 13  | 1μF 10%, 16V ceramic capacitors (1206)              | Panasonic                | ECJ-3YB1C105K   |

| C6, C62, C65                                                                                                                                                  | 3   | 0.001μF 10%, 50V ceramic capacitors (0603)          | Panasonic                | ECJ-1VB1H102K   |

| C7, C8, C9, C11,<br>C35, C58, C76                                                                                                                             | 7   | 68μF 20%, 16V tantalum capacitors (D case)          | Panasonic                | ECS-T1CD686R    |

| C12, C13                                                                                                                                                      | 2   | 10pF 5%, 50V ceramic capacitors (tall case)         | Phycomp                  | 1206CG100J9B200 |

| C45, C46                                                                                                                                                      | 2   | 10,000pF 10%, 16V ceramic capacitors (0603)         | Panasonic                | ECJ-1VB1C103K   |

| C63, C64, C67                                                                                                                                                 | 3   | 0.01μF 10%, 50V X7R ceramic capacitors (0603)       | AVX                      | 06035C103KAT    |

| C71, C72                                                                                                                                                      | 2   | 56,000pF 10%, 16V ceramic capacitors (0603)         | Panasonic                | ECJ-1VB1C563K   |

| D1, D2                                                                                                                                                        | 2   | 1A 50V general-purpose silicon diodes               | General<br>Semiconductor | 1N4001          |

| DS1, DS2,<br>DS6-DS10                                                                                                                                         | 7   | LED, green, SMD                                     | Panasonic                | LN1351C         |

| DS3, DS4, DS5,<br>DS11-DS19                                                                                                                                   | 12  | LED, red, SMD                                       | Panasonic                | LN1251C         |

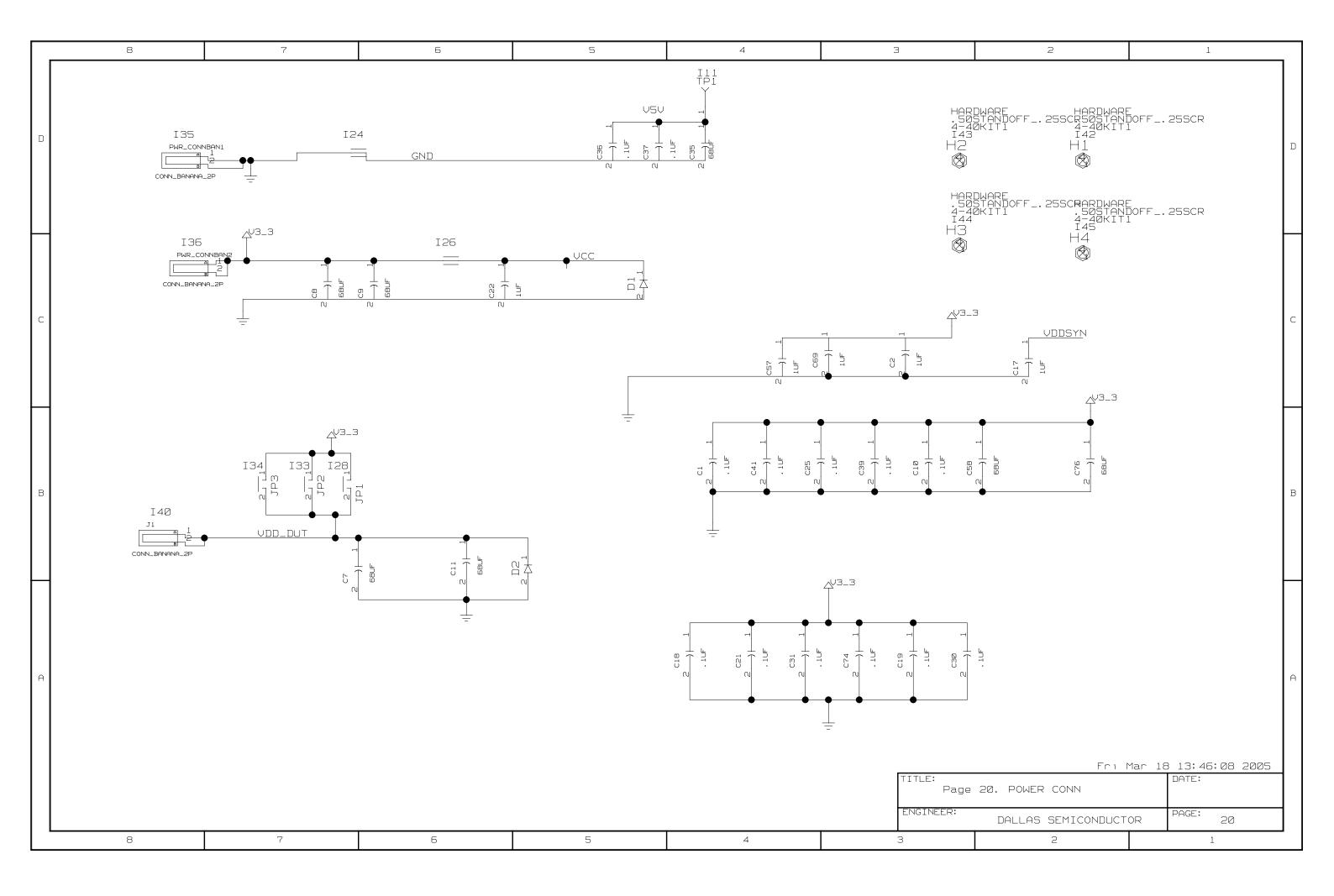

| J1,<br>PWR_CONNBAN1                                                                                                                                           | 2   | Banana plug sockets (horizontal, black)             | Mouser<br>Electronics    | 164-6218        |

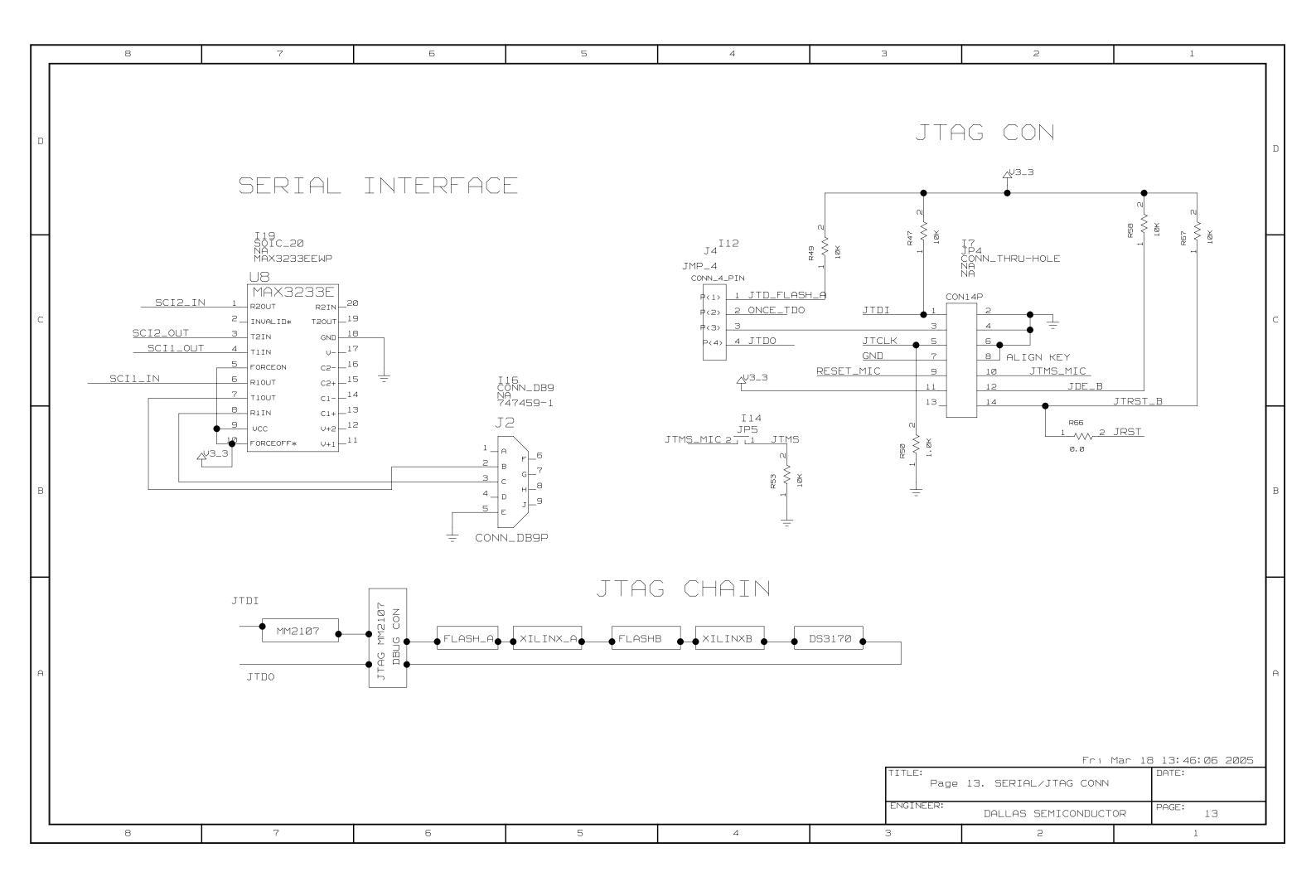

| J2                                                                                                                                                            | 1   | DB9 right-angle connector (long case)               | AMP                      | 747459-1        |

| J3                                                                                                                                                            | 1   | 50-pin, dual-row, vertical terminal strip           | Samtec                   | TSW-125-07-T-D  |

| J4                                                                                                                                                            | 1   | 100-mils 4-position jumper                          | Samtec                   | NA              |

| J5                                                                                                                                                            | 1   | $50\Omega$ BNC connector (5-pin right-angle header) | Trompeter                | CBJR220         |

| J6, J7                                                                                                                                                        | 2   | Terminal strip, 10-pin, dual row, vertical          | Samtec                   | NA              |

| J8, J9                                                                                                                                                        | 2   | $75\Omega$ BNC connectors (5-pin rightangle)        | Trompeter                | UCBJR220        |

| JP1, JP2, JP3,<br>JP5, JP7, JP8                                                                                                                               | 6   | 2-pin headers, 0.100" centerline (vertical)         | Samtec                   | TSW-102-07-T-S  |

| JP4                                                                                                                                                           | 1   | 14-pin connector (dual row, vertical)               | Samtec                   | NA              |

| JP6                                                                                                                                                           | 1   | 100-mils 3-position jumper                          | Samtec                   | NA              |

| L1                                                                                                                                                            | 1   | 1.0μH 20% 2-pin surface-mount inductor              | Coiltronics              | UP1B-1R0        |

| PWR_CONNBAN2                                                                                                                                                  | 1   | Banana plug socket (horizontal, red)                | Mouser<br>Electronics    | 164-6219        |

|                                                                                                                                                                                 |     | I                                                            | T                       |                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------|-------------------------|------------------|

| DESIGNATION                                                                                                                                                                     | QTY | DESCRIPTION                                                  | SUPPLIER                | PART NUMBER      |

| R1–R4, R12, R42,<br>R43, R54–R56,<br>R59, R63, R68,<br>R69, R70, R73,<br>R74, R83, R93,<br>R107                                                                                 | 20  | 150Ω 1%, 1/16W resistors (0603)                              | Panasonic               | ERJ-3EKF1500V    |

| R5–R8, R10, R15,<br>R51, R57, R62,<br>R71, R81, R85,<br>R92, R94, R95,<br>R100, R101,<br>R103–R106, R109                                                                        | 22  | 33Ω 5%, 1/16W resistors (0603)                               | Panasonic               | ERJ-3GEYJ330V    |

| R9, R11, R16,<br>R22, R30, R32,<br>R38, R46, R60,<br>R61, R64, R65,<br>R72, R77–R80,<br>R89, R90, R91,<br>R96                                                                   | 22  | $330\Omega$ 5%, 1/16W resistors (0603)                       | Panasonic               | ERJ-3GEYJ331V    |

| R13                                                                                                                                                                             | 1   | 1.0MΩ 5%, 1/16W resistor (0603)                              | Panasonic               | ERJ-3GEYJ105V    |

| R14, R17–R21,<br>R23–R29, R31,<br>R33–R37, R39,<br>R40, R41, R44,<br>R45, R47, R48,<br>R49, R52, R53,<br>R58, R67, R75,<br>R76, R82, R86,<br>R87, R98, R99,<br>R102, R108, R110 | 41  | 10kΩ 5%, 1/16W resistors (0603)                              | Panasonic               | ERJ-3GEYJ103V    |

| R50                                                                                                                                                                             | 1   | 1.0kΩ 5%, 1/16W resistor (0603)                              | Panasonic               | ERJ-3GEYJ102V    |

| R66, R88, R97                                                                                                                                                                   | 3   | 0Ω 1%, 1/16W resistors (0603)                                | AVX                     | CJ10-000F        |

| R84                                                                                                                                                                             | 1   | 51.1Ω 1%, 1/16W resistor (0603)                              | Panasonic               | ERJ-3EKF51R1V    |

| SW1, SW2, SW5                                                                                                                                                                   | 3   | 4-pin single-pole switch MOM                                 | Panasonic               | EVQPAE04M        |

| SW3, SW4                                                                                                                                                                        | 2   | 8-position switch,<br>16-pin DIP, low profile                | AMP                     | 435668-7         |

| SW6                                                                                                                                                                             | 1   | Slide switch (DPDT)<br>6-pin through-hole                    | Тусо                    | SSA22            |

| T1, T2                                                                                                                                                                          | 2   | 1:2 XFMR T3/E3/STS-1 (industrial)                            | Pulse                   | T3012            |

| TP1-TP24                                                                                                                                                                        | 24  | Test points, compensated, 3pF, 953 $\Omega$ , 3 plated holes | NA                      | KIT1             |

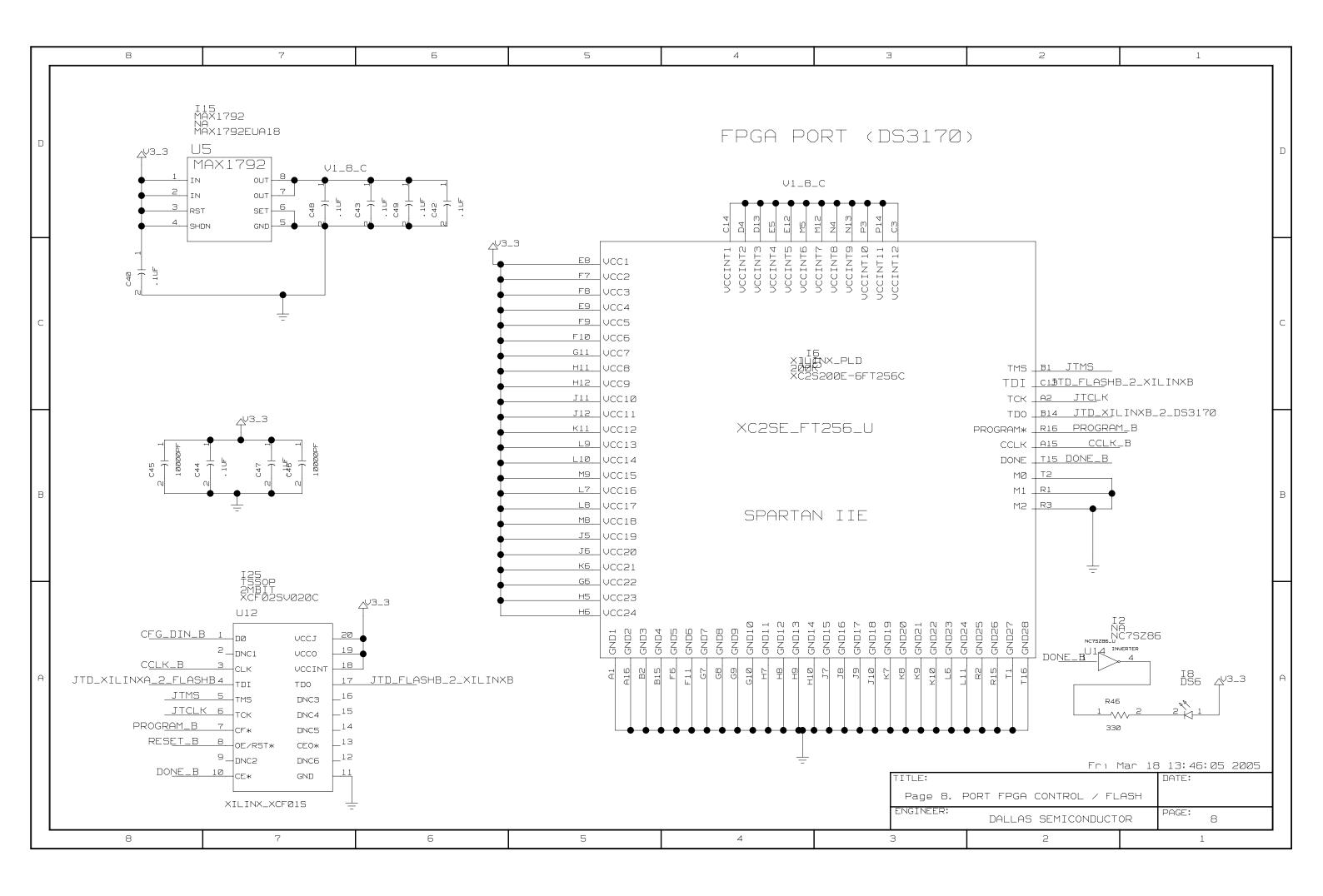

| U1, U5                                                                                                                                                                          | 2   | 8-pin power-μMAX (1.8V or Adj)                               | Maxim                   | MAX1792EUA18     |

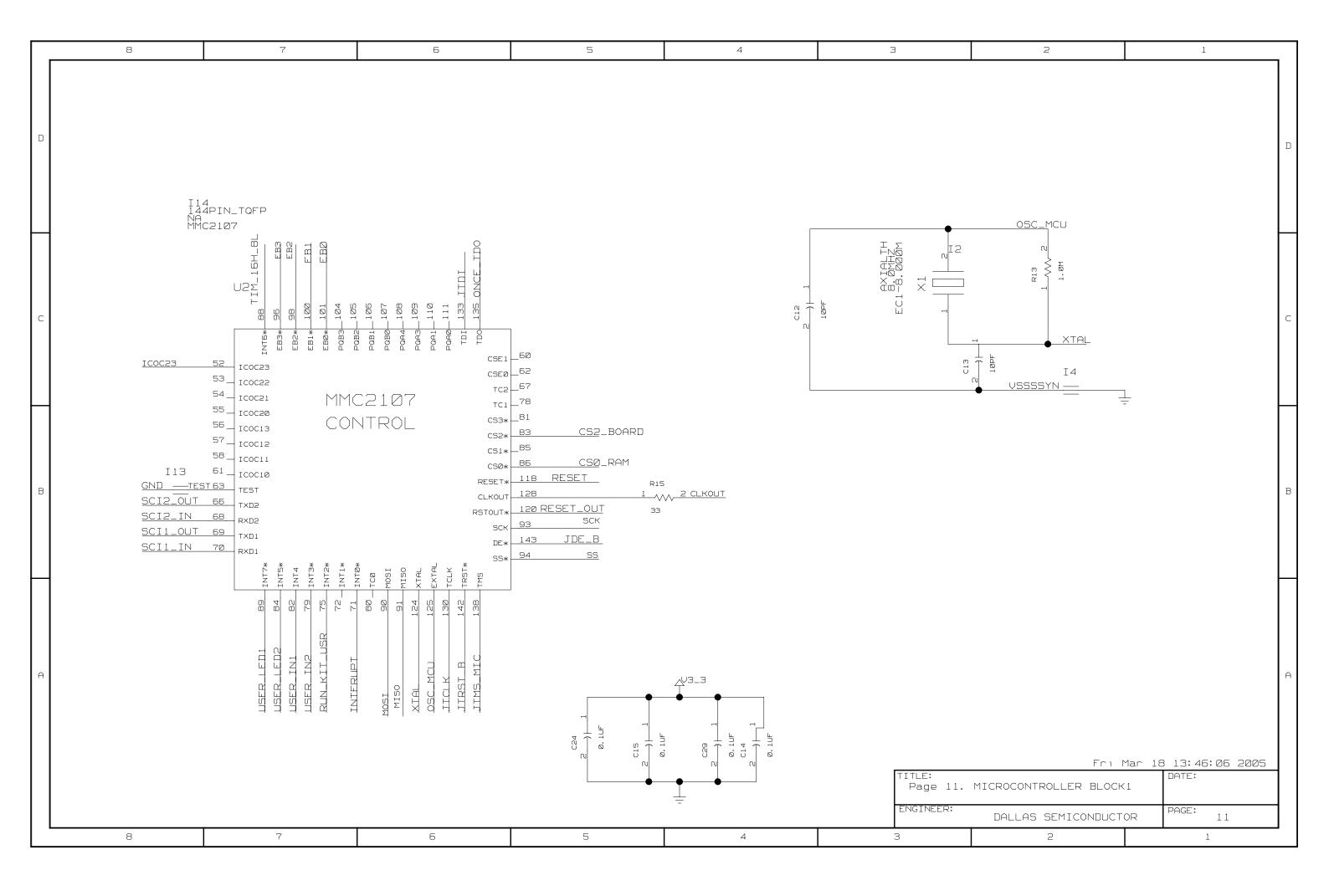

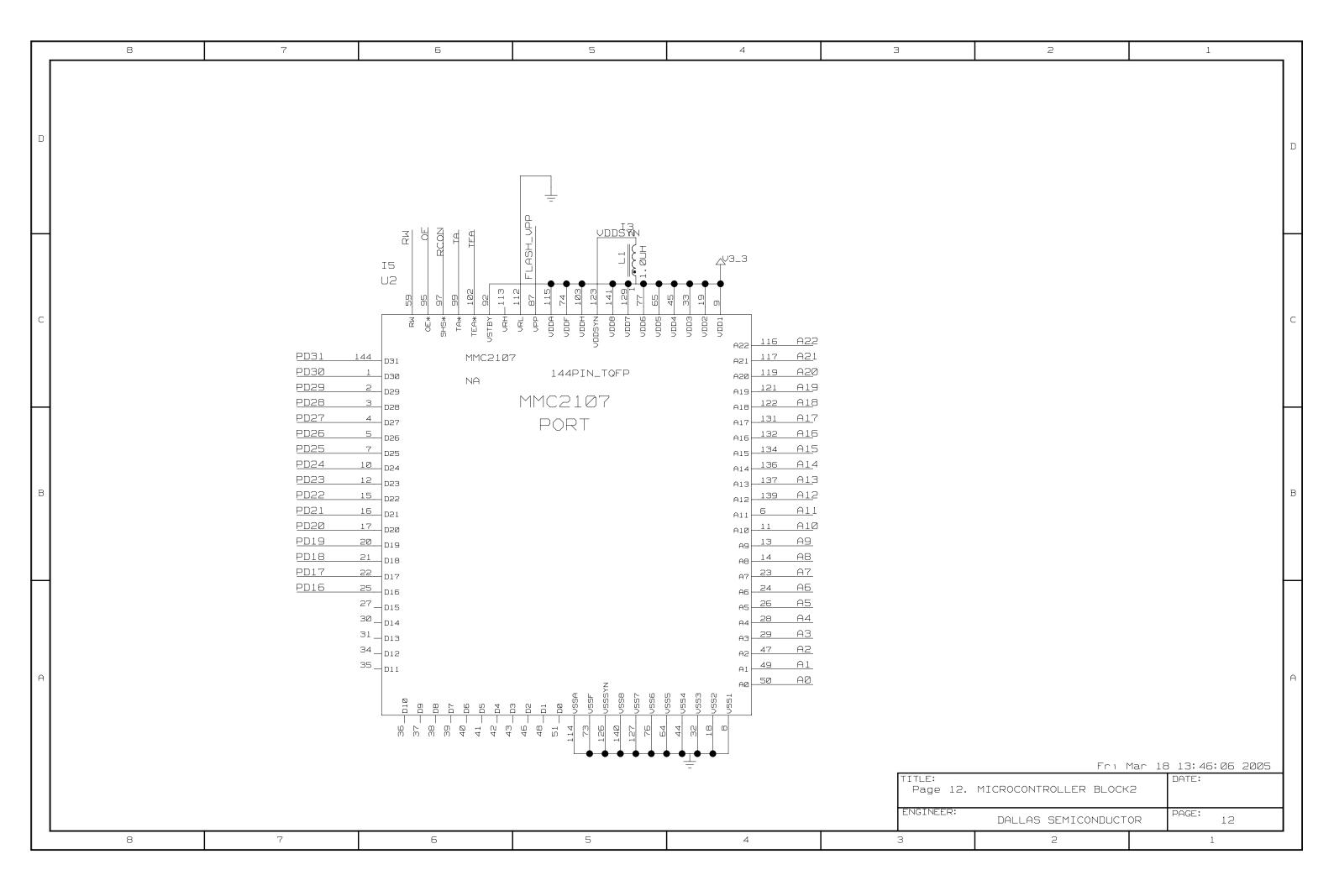

| U2                                                                                                                                                                              | 1   | M-CORE 32-bit microcontroller                                | Motorola                | MMC2107          |

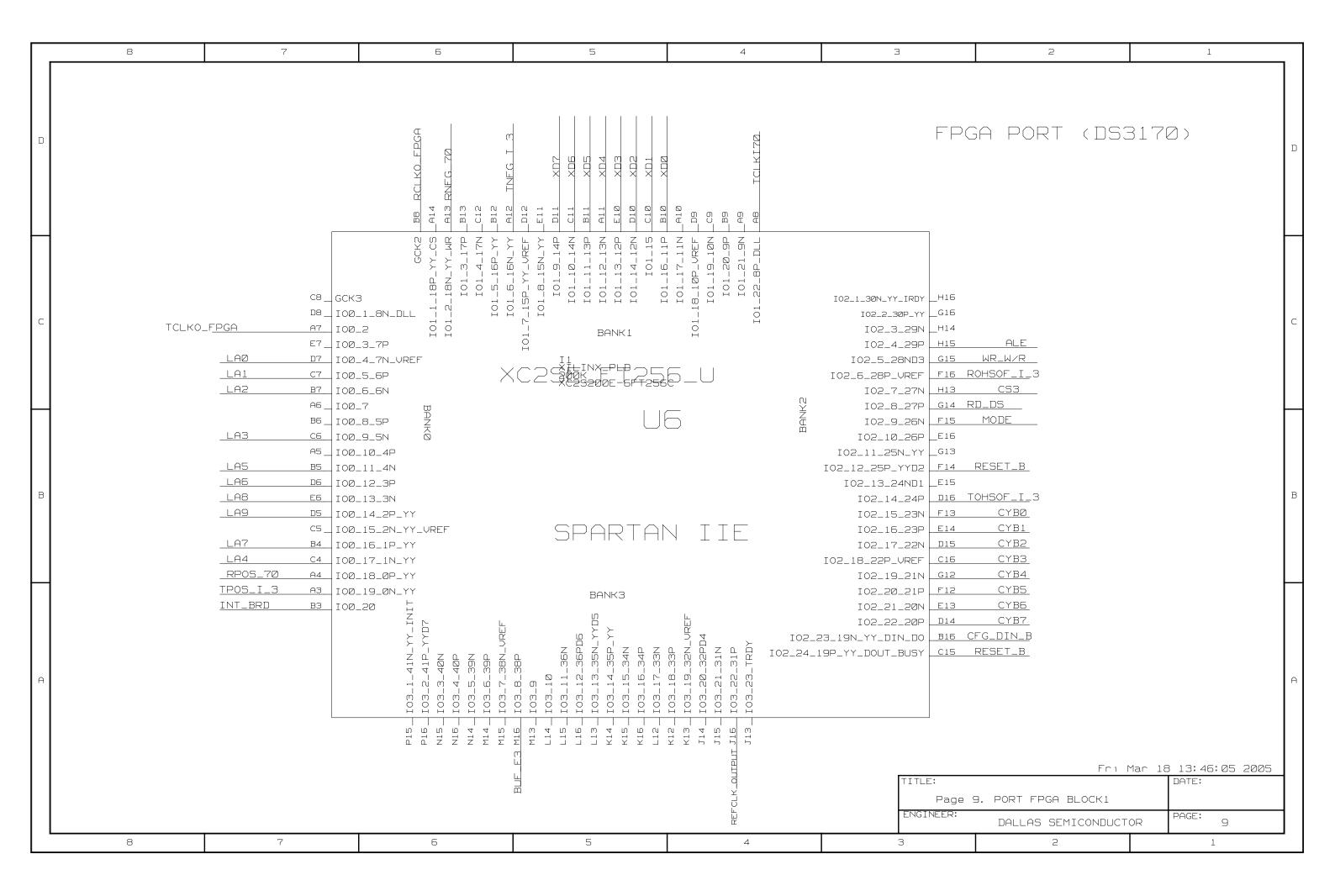

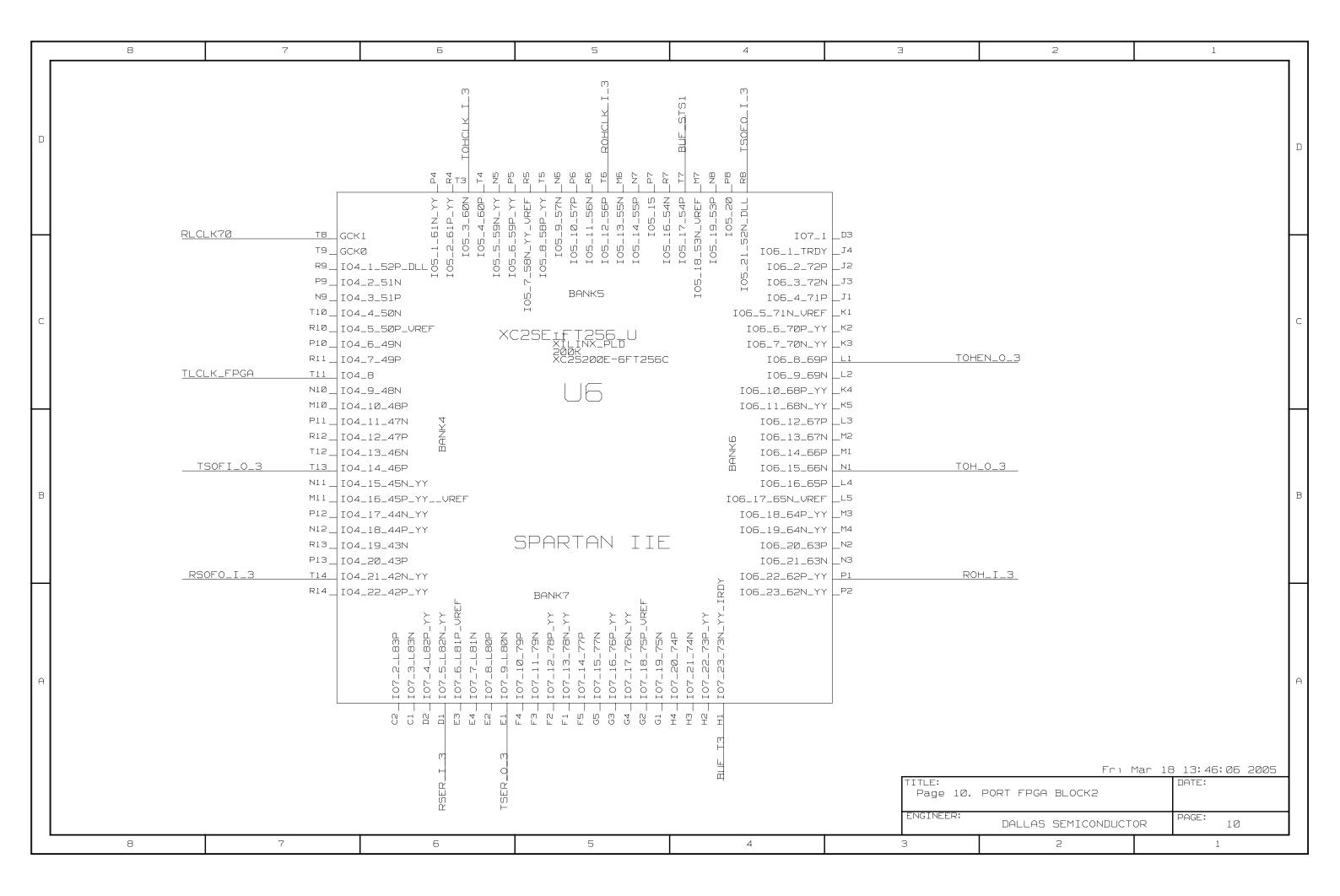

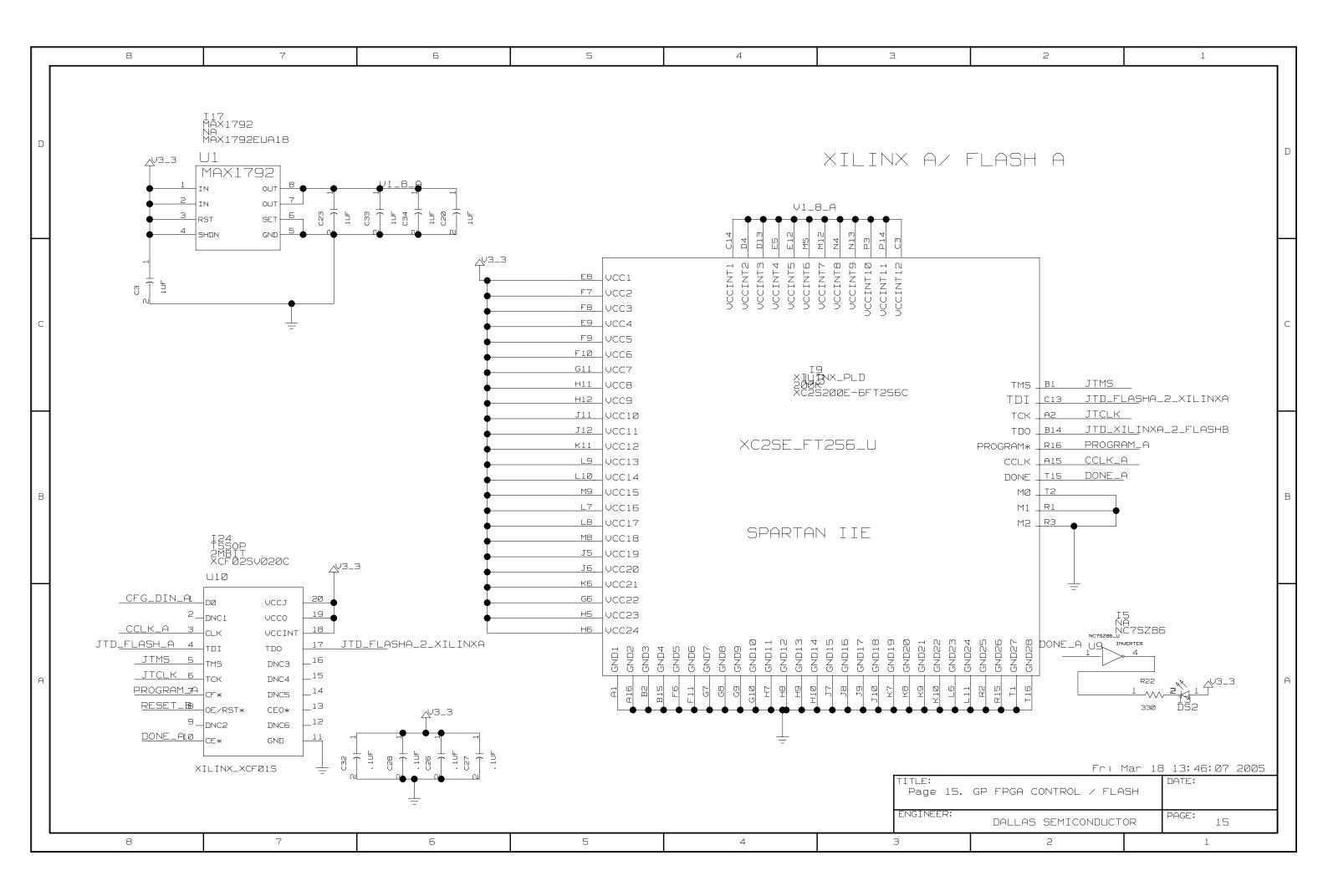

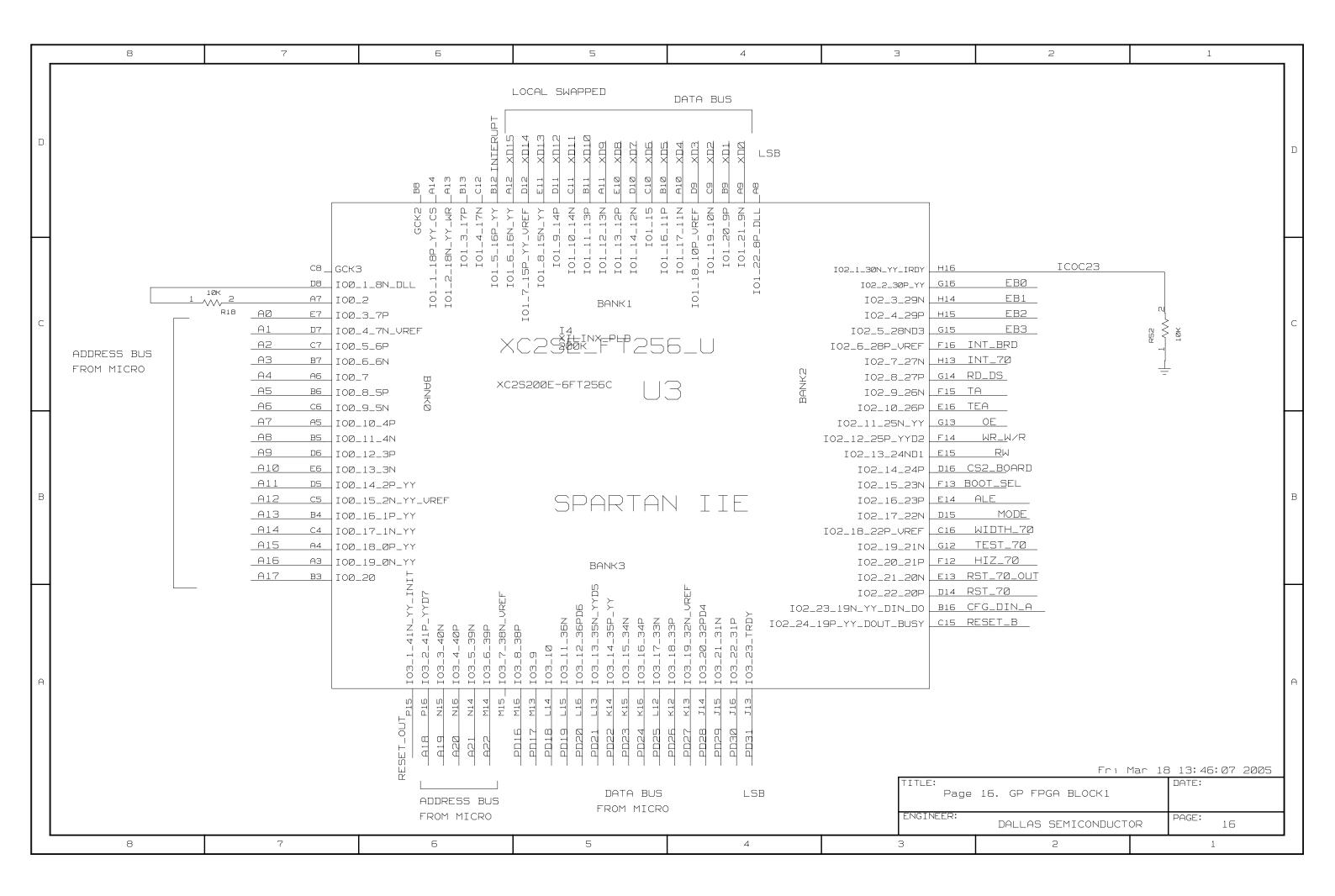

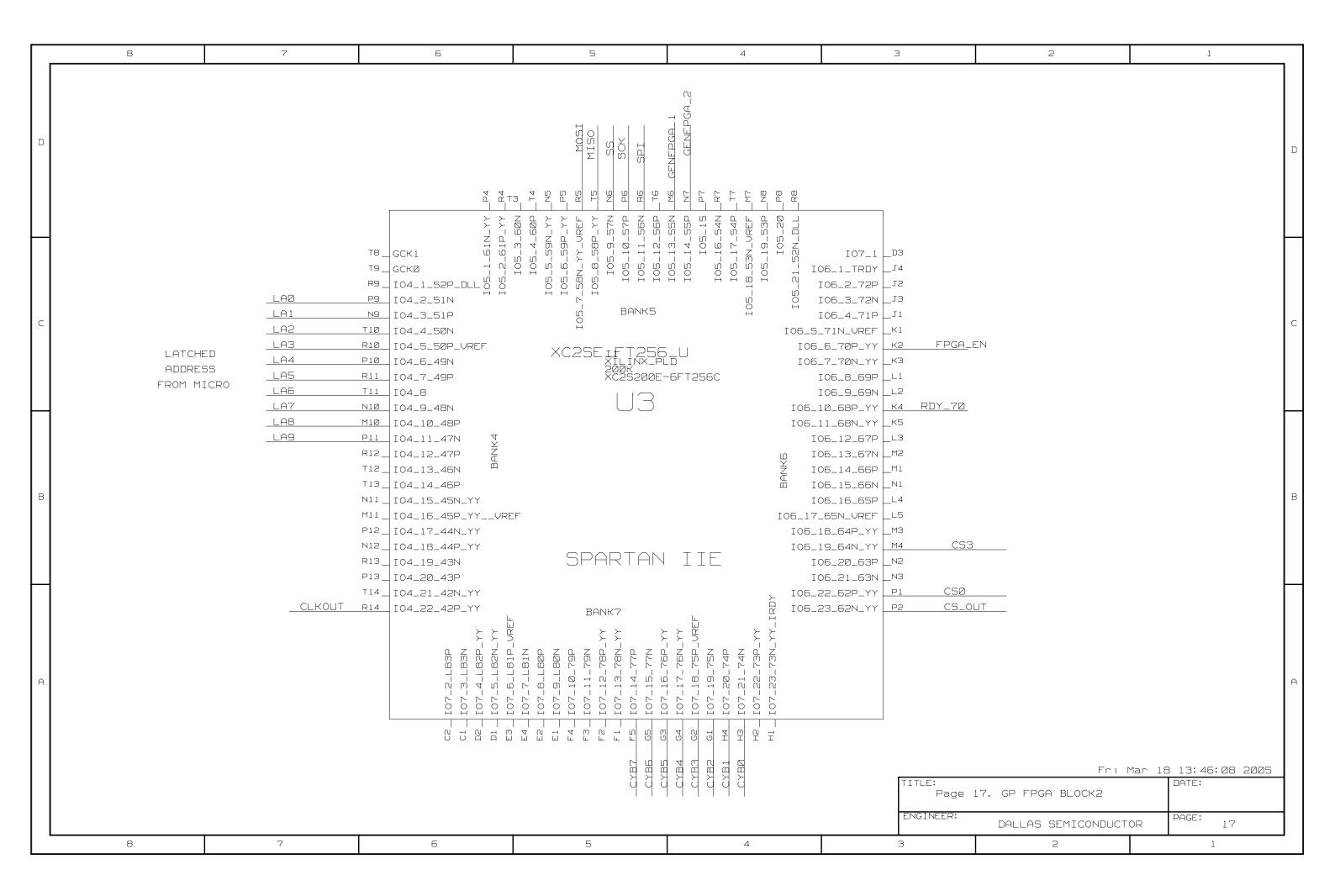

| U3, U6                                                                                                                                                                          | 2   | Spartan-IIE 200K gate, 1.8V FPGA, 256 PIN BGA                | Xilinx                  | XC2S200E-6FT256C |

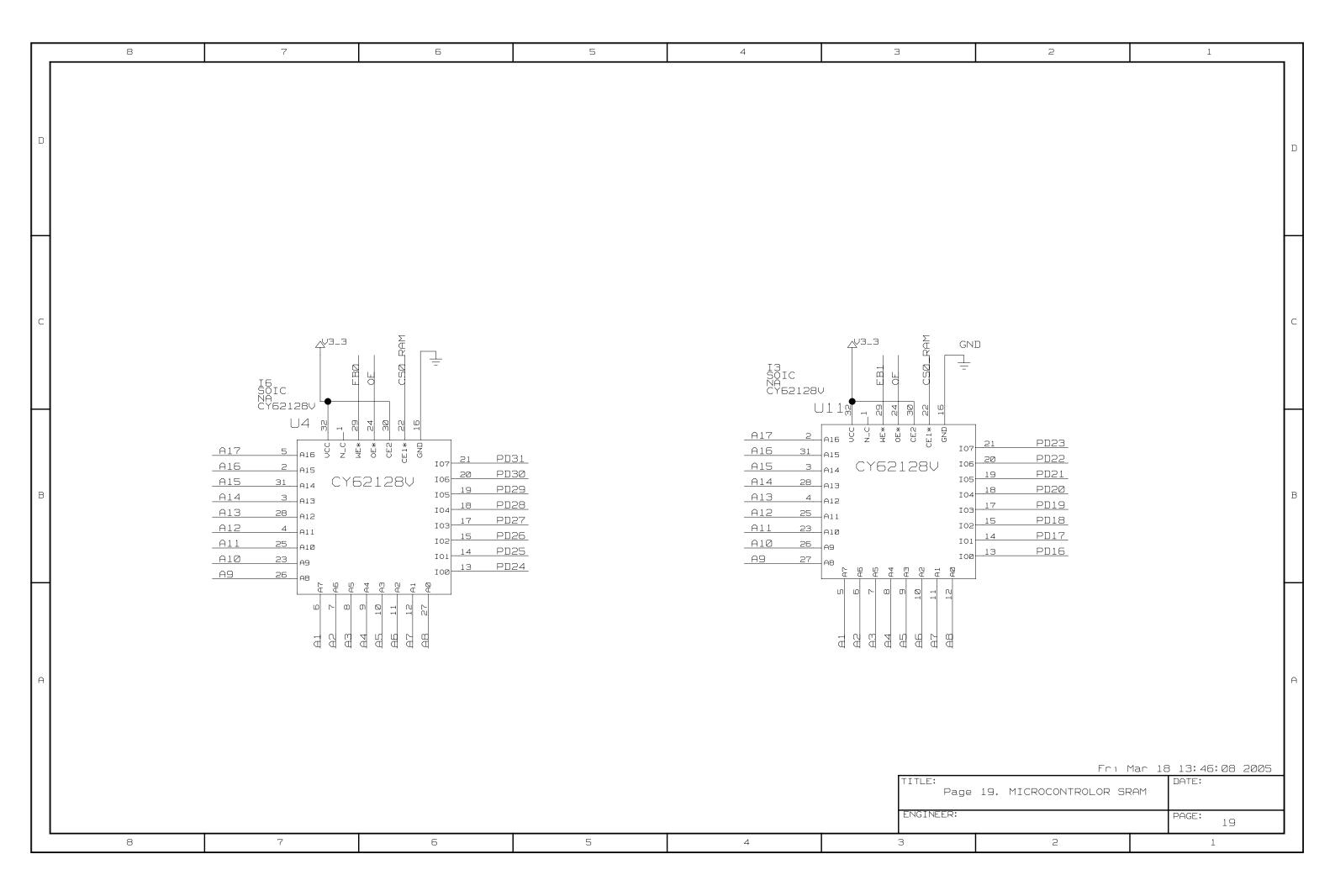

| U4, U11                                                                                                                                                                         | 2   | 128K x 8 SRAM                                                | Cypress                 | CY62128V         |

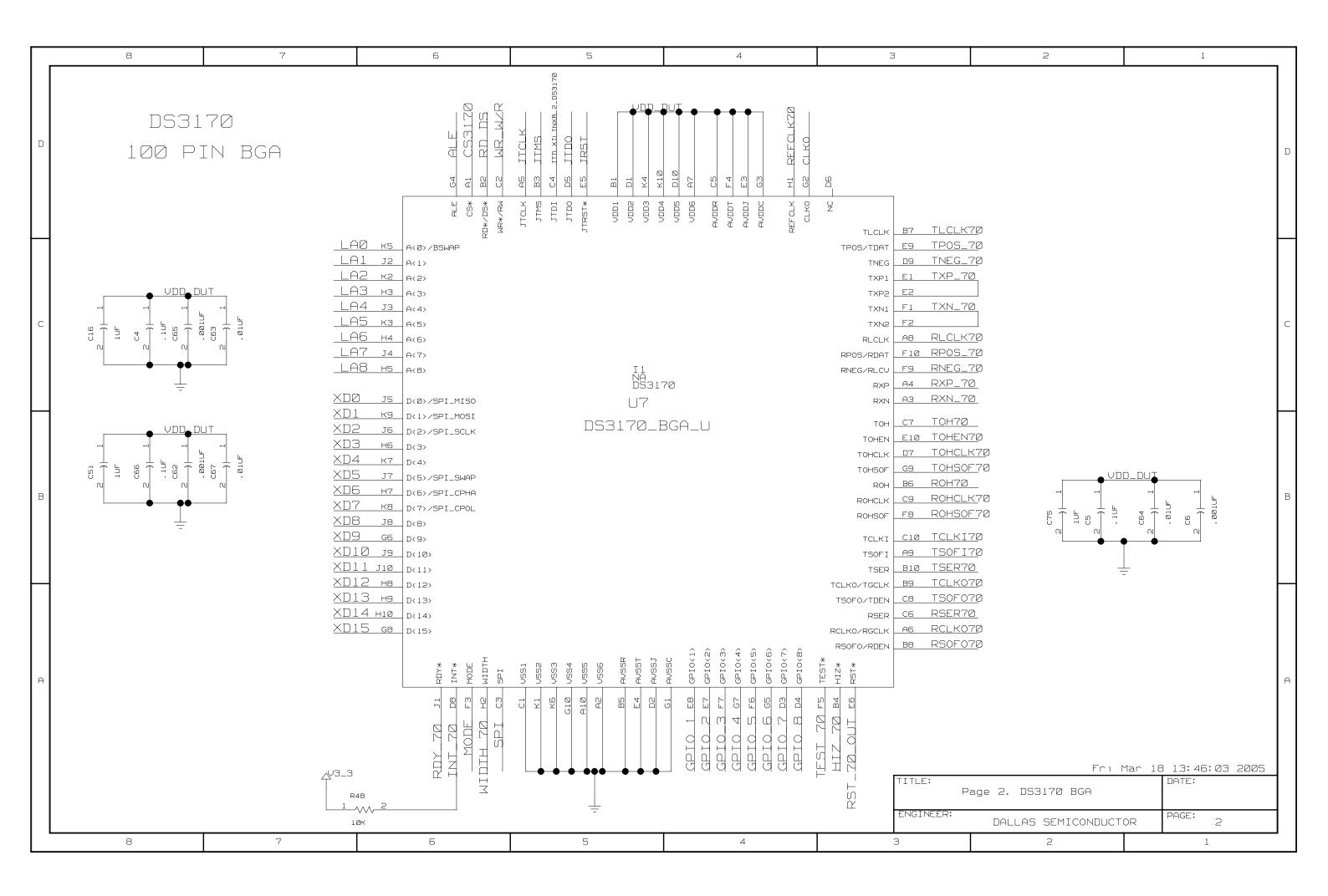

| U7                                                                                                                                                                              | 1   | DS3/E3 SCT<br>100-pin CSBGA (11mm x 11mm)                    | Dallas<br>Semiconductor | DS3170           |

| U8                                                                                                                                                                              | 1   | 3.3V RS-232<br>20-pin SO                                     | Maxim                   | MAX3233EEWP      |

| U9, U14, U16–<br>U20, U23                                                                                                                                                       | 8   | High-speed buffer                                            | Fairchild               | NC7SZ86          |

| DESIGNATION   | QTY | DESCRIPTION                              | SUPPLIER        | PART NUMBER      |

|---------------|-----|------------------------------------------|-----------------|------------------|

| U10, U12      | 2   | 2Mb flash-based configuration memory     | Xilinx          | XCF02SV020C      |

| U13           | 1   | Quad 2-input NAND gate<br>14-pin SO      | Toshiba         | TC74HC00AFN      |

| U15, U21, U24 | 3   | Hex inverter, SO                         | Toshiba         | TC74HC04AFN      |

| U22           | 1   | SOT switch debouncer                     | Maxim           | MAX6816          |

| X1            | 1   | 8.0MHz low-profile crystal               | Dove Electronic | EC1-8.000M       |

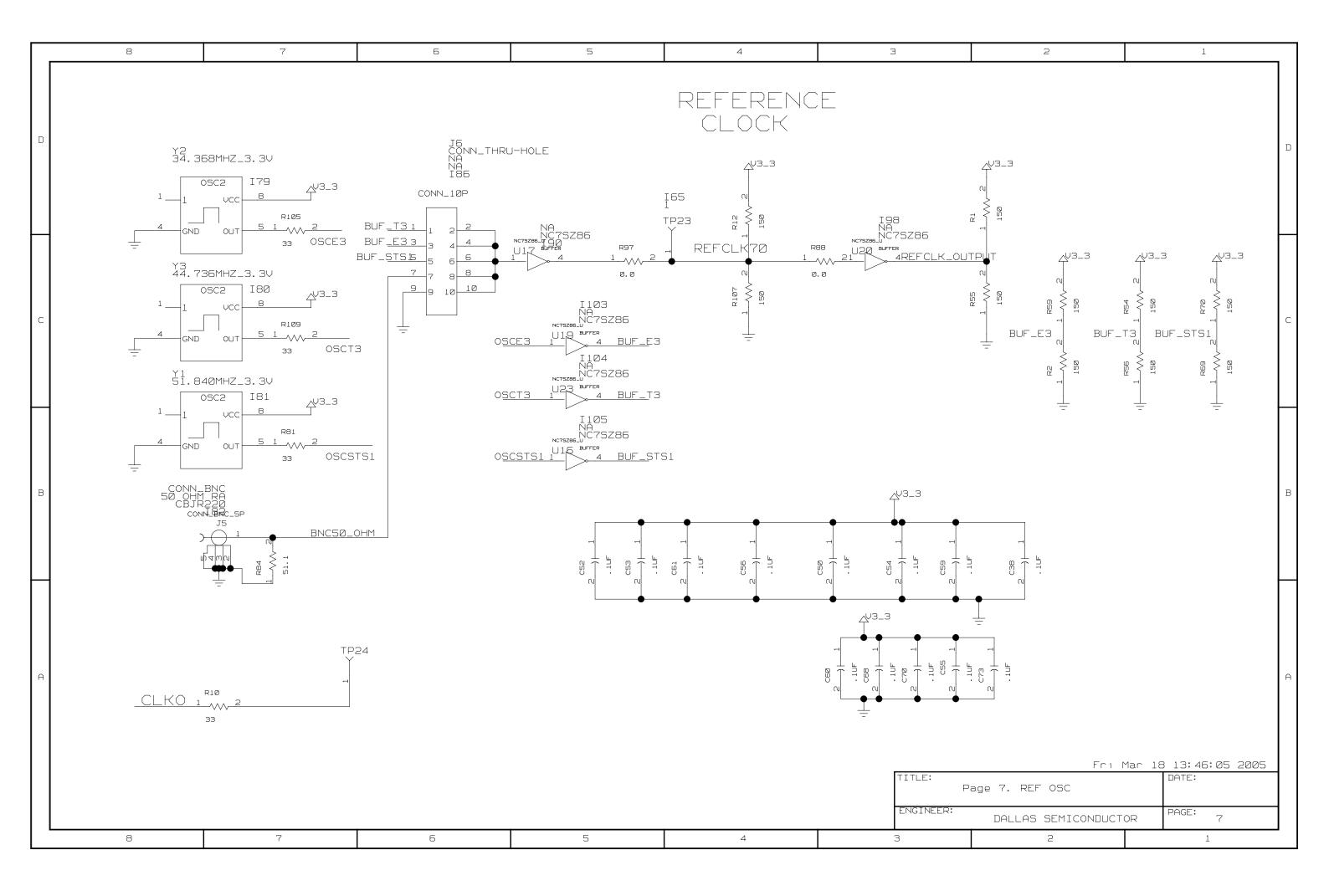

| Y1            | 1   | 3.3V 51.840MHz oscillator, crystal clock | SaRonix         | NTH089AA3-51.840 |

| Y2            | 1   | 3.3V 34.368MHz oscillator, crystal clock | SaRonix         | NTH089AA3-34.368 |

| Y3            | 1   | 3.3V 44.736MHz oscillator, crystal clock | SaRonix         | NTH089AA3-44.736 |

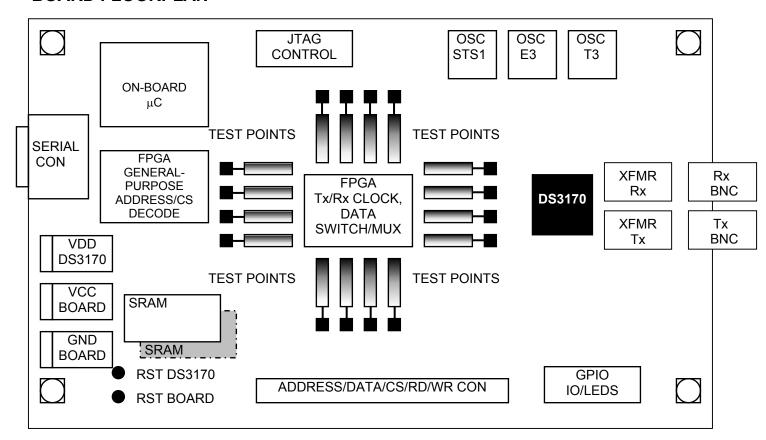

## **BOARD FLOORPLAN**

### **BASIC OPERATION**

This design kit relies upon several supporting files, which are available for downloading on our website at <a href="https://www.maxim-ic.com/telecom">www.maxim-ic.com/telecom</a>. See the DS3170DK QuickView page for files.

The support files are used with an evaluation program called ChipView with is available for download at www.maxim-ic.com/telecom.

#### HARDWARE CONFIGURATION

## **Quick Start (Hardware Settings)**

- For single power-supply operation, short jumpers JP1-JP3. This connects VDD of the DS3170 to the board VCC.

- Ensure that PROGRAM FLASH MICRO is selected (SW6). DS3 should not be on.

- Connect reference clock. See <u>Table 1</u>.

- DIP switches (SW3) can be in either the ON or OFF position depending on the desired configuration. See Table 6..

- Connect serial cable from DS3170DK (J2) to PC.

- Supply 3.3V to the banana-plug receptacles marked GND and VCC\_3.3V.

## **Reference Clock Configuration**

The reference clock for the DS3170 (SCT) can be configured a number of ways depending on the application's need. This is done by shorting the REFCLK signal on J6 to the signal inputs, which are also connected to J6.

Table 1: Reference Clock Configuration

| REFERENCE<br>CLOCK | DESCRIPTION                                                    |

|--------------------|----------------------------------------------------------------|

| GND                | Short pins J6.1 and J6.2 together. Open all other pins on J6.  |

| BNC Input          | Short pins J6.3 and J6.4 together. Open all other pins on J6.  |

| STS1 OSC           | Short pins J6.5 and J6.6 together. Open all other pins on J6.  |

| E3 OSC             | Short pins J6.7 and J6.8 together. Open all other pins on J6.  |

| T3 OSC             | Short pins J6.9 and J6.10 together. Open all other pins on J6. |

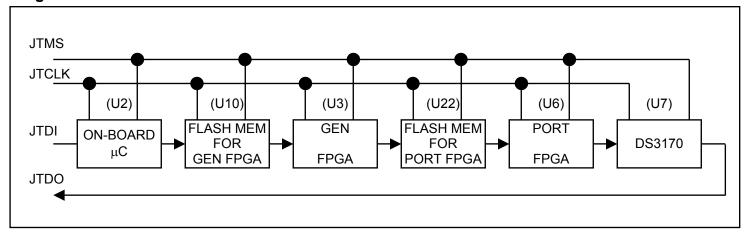

## **JTAG Configuration**

The JTAG chain is controlled by the following connectors: J4, JP4, and JP5. Depending on the function, such as programming the internal microcontroller flash or performing boundary scan operations, the three connectors can be configured to accomplish the desired task. For information on programming the internal flash of the microcontroller, refer to the microcontroller user manual and board schematic.

For most purposes, having the complete JTAG chain is sufficient. Figure 1 shows the complete chain as well as what order the devices will appear during boundary scan. To set up this configuration, perform the following:

- Connect JTDI to JP4.1

- Connect JTDO to JP4.3

- Connect JTMS to JP4.10

- Connect JCLK to JP4.5

- Connect J4.1 to J4.2

- Connect J4.3 to J4.4

- Connect JP5.1 to JP5.2

Figure 1. JTAG Chain

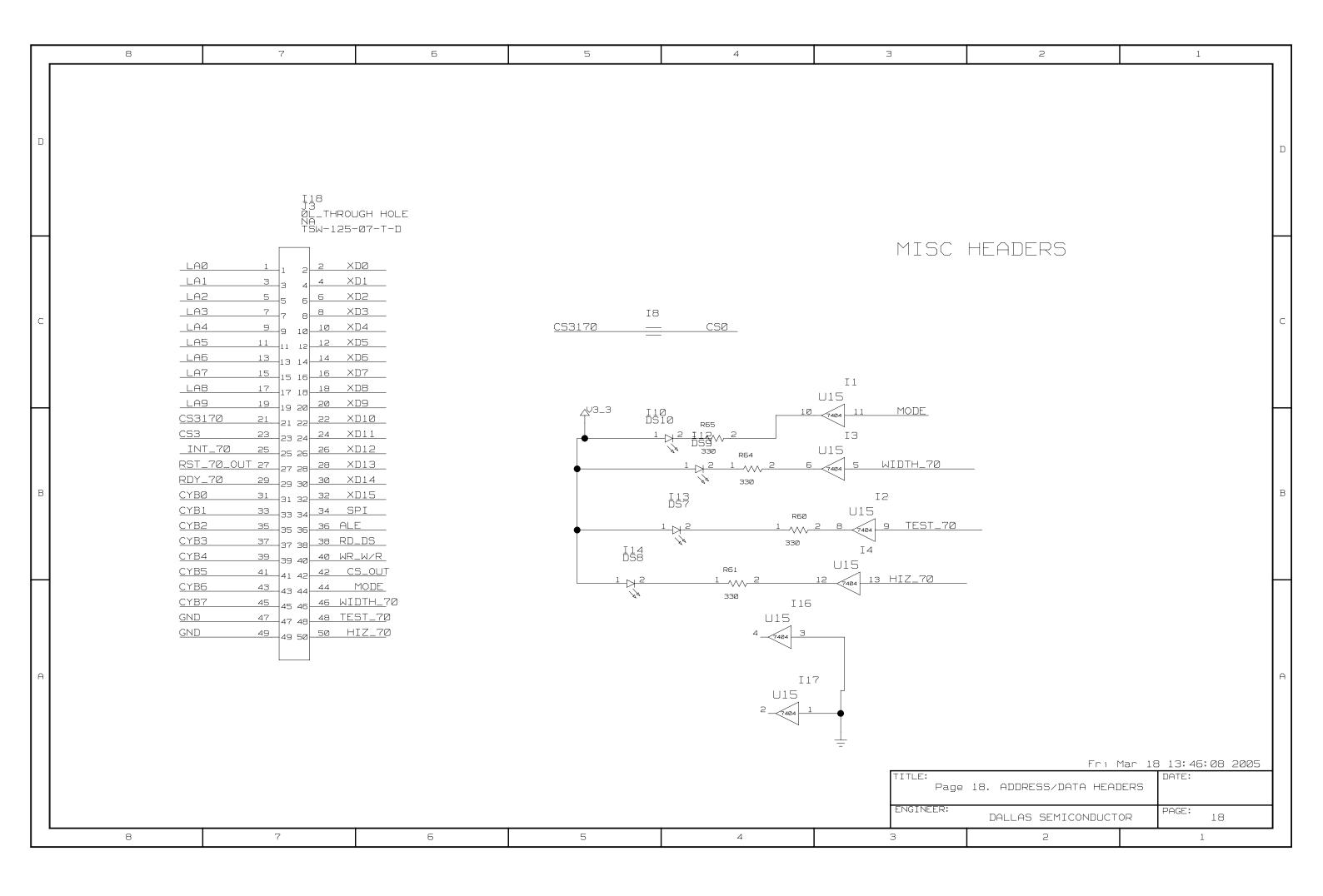

## Address/Data BUS Connector

The DS3170DK has a connector (J3) to monitor all local bus activity for the design kit. All the signals can be captured with a high-impedance probe and displayed on an oscilloscope or logic analyzer. **Note:** If FPGA\_ENABLE (SW3.3) is logic 0, the on-board microcontroller will no longer drive any data onto the local bus. Therefore, the user can now connect the local bus of the DS3170 into another system without making any modifications to the hardware. See Table 2 for specific pin information for connector J3.

Table 2. Address/Data Connector

| PIN<br>NUM | PIN<br>NAME | DESCRIPTION            | PIN<br>NUM | PIN<br>NAME | DESCRIPTION                     |

|------------|-------------|------------------------|------------|-------------|---------------------------------|

| 1          | A0          | Local Address Bit 0    | 2          | D0          | Local Data Bit 0                |

| 3          | A1          | Local Address Bit 1    | 4          | D1          | Local Data Bit 1                |

| 5          | A2          | Local Address Bit 2    | 6          | D2          | Local Data Bit 2                |

| 7          | A3          | Local Address Bit 3    | 8          | D3          | Local Data Bit 3                |

| 9          | A4          | Local Address Bit 4    | 10         | D4          | Local Data Bit 4                |

| 11         | A5          | Local Address Bit 5    | 12         | D5          | Local Data Bit 5                |

| 13         | A6          | Local Address Bit 6    | 14         | D6          | Local Data Bit 6                |

| 15         | A7          | Local Address Bit 7    | 16         | D7          | Local Data Bit 7                |

| 17         | A8          | Local Address Bit 8    | 18         | D8          | Local Data Bit 8                |

| 19         | A9          | Local Address Bit 9    | 20         | D9          | Local Data Bit 9                |

| 21         | CS3170      | Chip Select DS3170     | 22         | D10         | Local Data Bit 10               |

| 23         | CSFPGA      | Chip Select Port FPGA  | 24         | D11         | Local Data Bit 11               |

| 25         | INT3170     | INT PIN DS3170         | 26         | D12         | Local Data Bit 12               |

| 27         | RST3170     | RST PIN DS3170         | 28         | D13         | Local Data Bit 13               |

| 29         | RDY         | Ready Handshake DS3170 | 30         | D14         | Local Data Bit 14               |

| 31         | TEST0       | Generic I/O Bit 0      | 32         | D15         | Local Data Bit 15               |

| 33         | TEST1       | Generic I/O Bit 1      | 34         | SPI         | DS3170 Serial/Parallel Bus Mode |

| 35         | TEST2       | Generic I/O Bit 2      | 36         | ALE         | Address Latch Enable            |

| 37         | TEST3       | Generic I/O Bit 3      | 38         | RD_DS       | Read (Intel)/Data Strobe (MOT)  |

| 39         | TEST4       | Generic I/O Bit 4      | 40         | WR_W/R      | Write (Intel)/Write_READ (MOT)  |

| 41         | TEST5       | Generic I/O Bit 5      | 42         | CS_OUT      | Programmable CS_OUT Pin         |

| 43         | TEST6       | Generic I/O Bit 6      | 44         | MODE        | Mot/Intel Mode                  |

| 45         | TEST7       | Generic I/O Bit 7      | 46         | WIDTH       | Data Bus Width                  |

| 47         | GND         | GND                    | 48         | TEST        | Test Enable (Active Low)        |

| 49         | GND         | GND                    | 50         | HIZ         | High Impedance (Active Low)     |

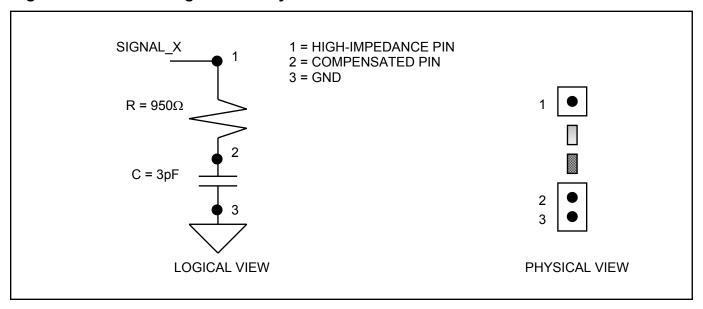

## **High Impedance and Compensated Test Points**

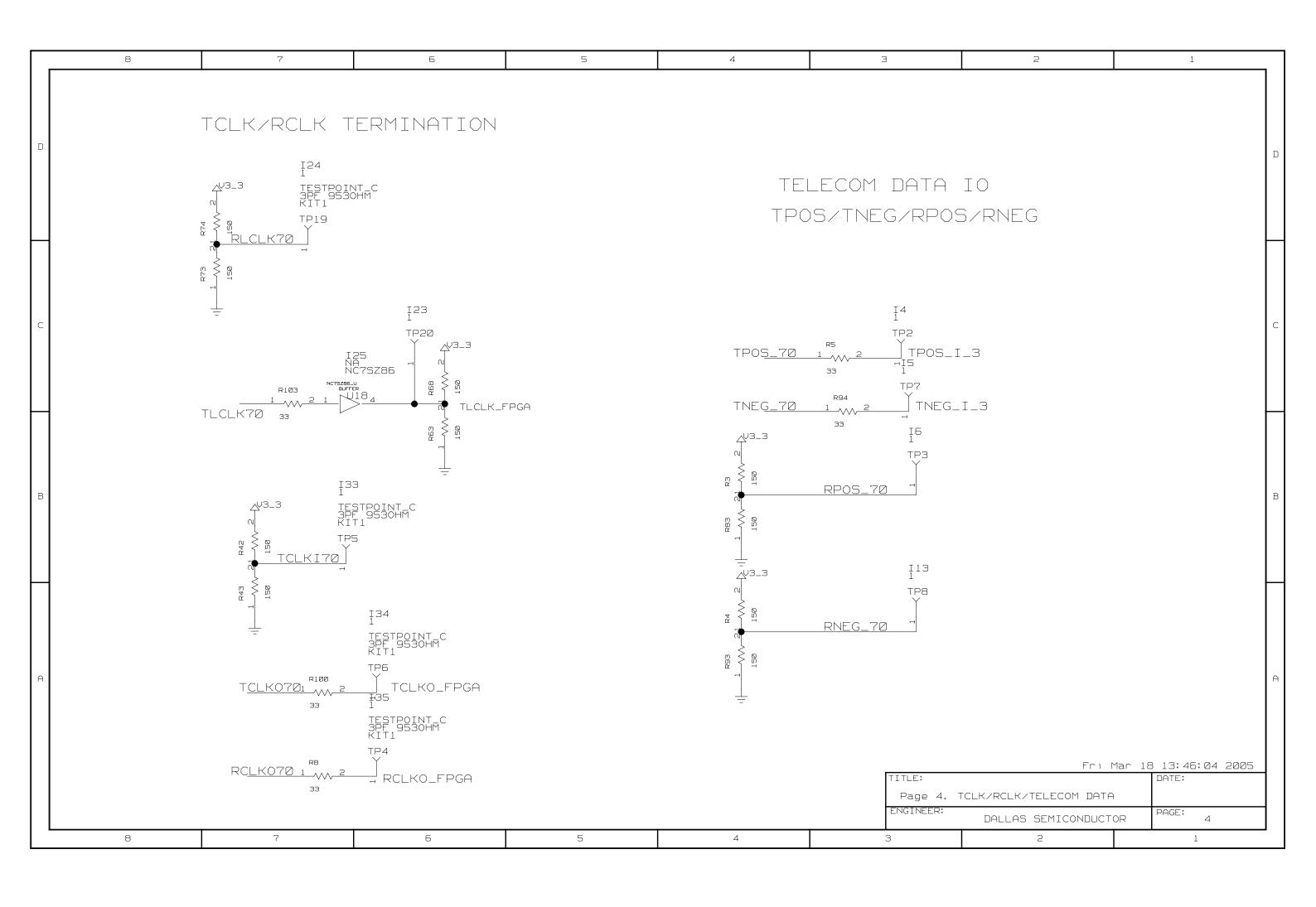

The test points for all the clock and data lines are unique for this board such that each test point listed in <u>Table 3</u> have a relative high-impedance pin and a compensated pin. The compensated pin is part of a (20:1) voltage divider that when used with the standard  $50\Omega$  load of an oscilloscope provides a very clean signal. If you are making critical timing and or slew rate measurements, the compensated test points are very useful. <u>Figure 2</u> shows the relationship between the high-impedance and compensated test point pins.

Figure 2. Test Point Logical and Physical View

**Table 3. Test Points**

| REF<br>DES | SIGNAL<br>NAME | REF<br>DES | SIGNAL<br>NAME |

|------------|----------------|------------|----------------|

| TP5        | TCLKI          | TP7        | TNEG           |

| TP6        | TCLKO          | TP8        | RNEG           |

| TP4        | RCLKO          | TP2        | TPOS           |

| TP20       | TLCLK          | TP3        | RPOS           |

| TP19       | RLCLK          | TP11       | TSER           |

| TP10       | TOHSOF         | TP9        | RSER           |

| TP12       | ROHSOF         | TP13       | TOHEN          |

| TP16       | TOHCLK         | TP14       | TOH            |

| TP17       | ROHCLK         | TP15       | ROH            |

| TP19       | TSOFO          | TP23       | REFCLK         |

| TP22       | RSOFO          | TP21       | TSOFI          |

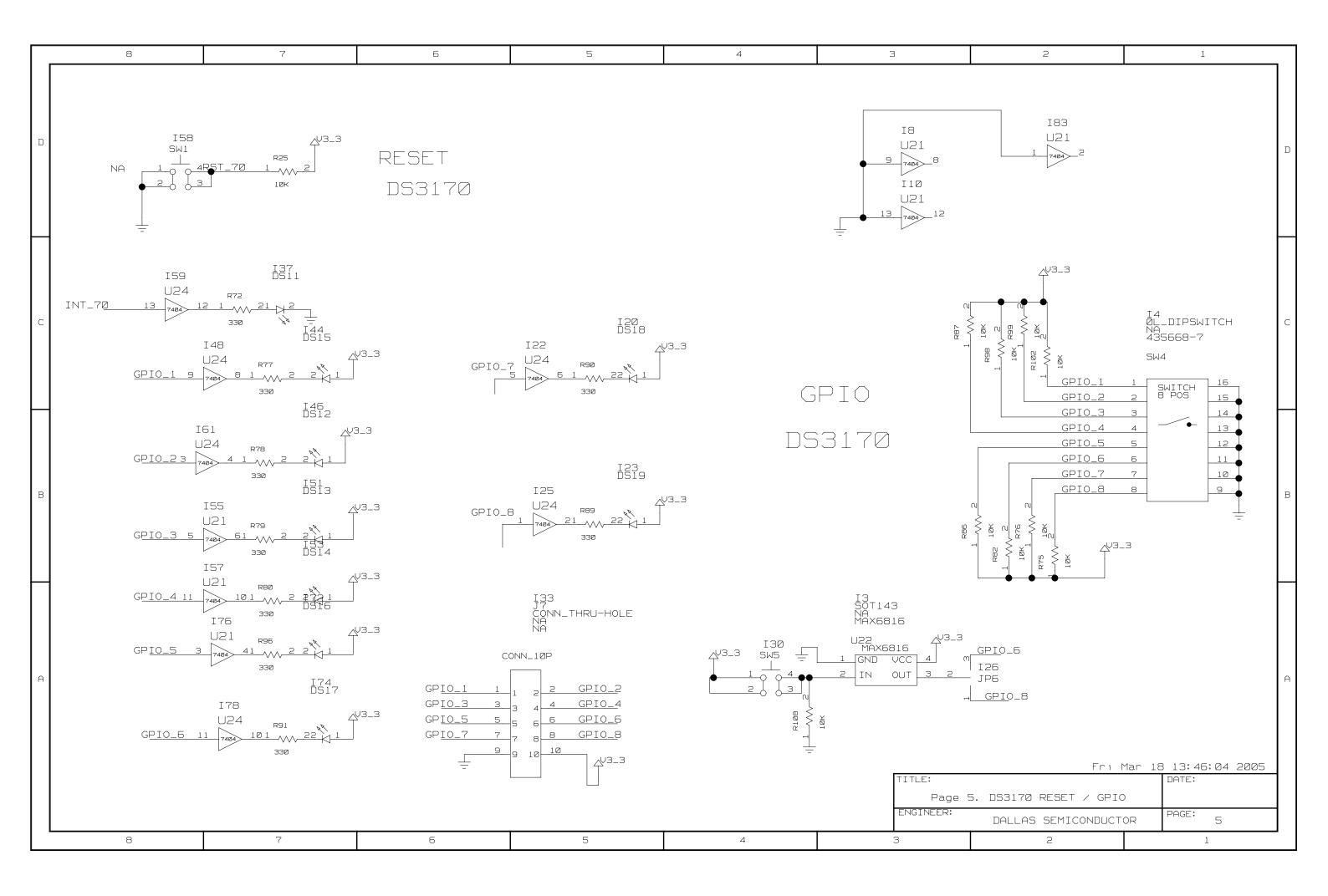

## **General Purpose Input/Output for DS3170**

The DS3170 SCT has an 8-bit port that can be bit configured as either general-purpose I/O or specific alarms, a TEMI input, or PMU input. Refer to the DS3170 data sheet for specific questions about the operation of the DS3170 GPIO port.

Each GPIO pin has two types of inputs and an LED for easy identification of the pin's state. The first input type for the GPIO port is an 8-bit switch (SW4). Each pin on SW4 corresponds to the bit in the GPIO. When the switch is in the "On" position, the pin for the switch is grounded and provides logic 0 to the port. When the switch is in the "Off" position, the pin for the switch floats to VDD and provides logic 1 to the port.

The second input type for the GPIO port is a straight 10-pin header (J7). This can be simply a monitoring pin for the GPIO port or used as input stimulus. **Note:** If you plan to drive a bit to a value other than GND, the GPIO bit in SW4 must be in the "Off" position. See the DS3170DK schematic for questions on the connection of the GPIO port.

Table 4 provides a description of pin out of SW4 and J7.

**Table 4. GPIO Header and Switch Pinout**

| PIN NU | MBER | PIN NAME   |

|--------|------|------------|

| SW4.1  | J7.1 | GPIO Bit 1 |

| SW4.2  | J7.2 | GPIO Bit 2 |

| SW4.3  | J7.3 | GPIO Bit 3 |

| SW4.4  | J7.4 | GPIO Bit 4 |

| SW4.5  | J7.5 | GPIO Bit 5 |

| SW4.6  | J7.6 | GPIO Bit 6 |

| SW4.7  | J7.7 | GPIO Bit 7 |

| SW4.8  | J7.8 | GPIO Bit 8 |

## **TEMI and PMU Inputs**

GPIO Bit 6 and GPIO Bit 8 can be configured to be the TEMI and PMU inputs respectively. A pushbutton (SW5) and 3-position jumper (JP6) are available to provide a glitch-free input to either of these inputs. **Note:** When using the pushbutton (SW5) and 3-position jumper (JP6) as an input to the GPIO pins, you must have the appropriate switch in SW4 in the "Off" position.

Table 5. TEMI and PMU Configuration

| SIGNAL<br>NAME | SETUP PROCEDURE                 |

|----------------|---------------------------------|

| TEMI           | Set SW4.6 to the "Off" position |

| I EIVII        | Short (Jumper) JP6.3 and JP2    |

| PMU            | Set SW4.8 to the "Off" position |

|                | Short (Jumper) JP6.1 and JP2    |

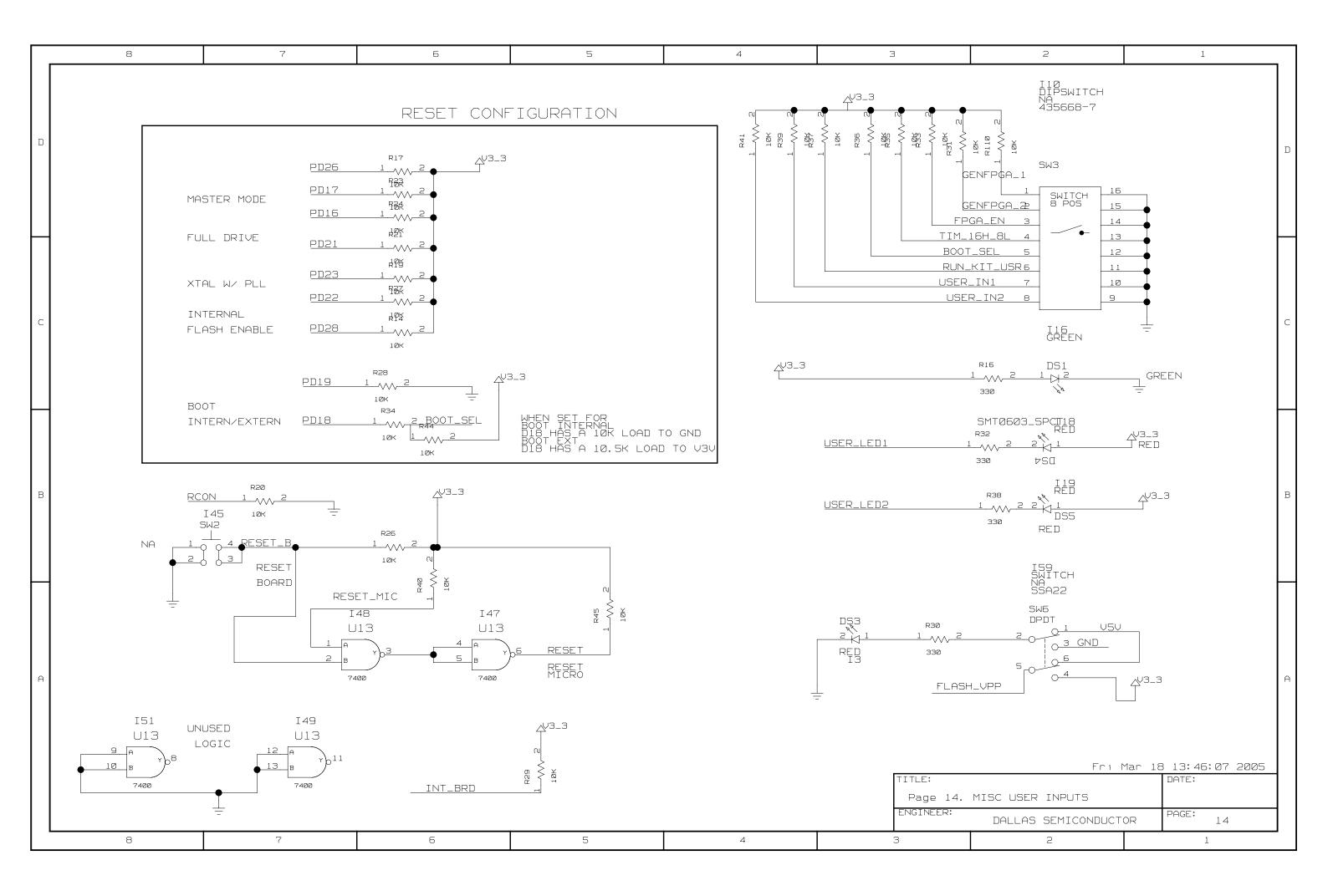

## **User Input Switch (SW3)**

SW3 is an 8-pin DIP switch that controls the function of the on-board microcontroller and the two on-board FPGAs, and offers a number of generic inputs for user programs.

**Table 6. User Input Switch Pinout**

| PIN | NAME                  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | FPGA<br>INPUT 1       | Generic Input-Only Pin to the General-Purpose FPGA. Value of pin is copied to general-purpose register XXXXXXXXX. Can be used for user programs. This pin has no effect if FPGA ENABLE is logic 0.                                                                                                                                                                                                                                                                                                                                                                  |

| 2   | FPGA<br>INPUT 2       | Generic Input-Only Pin to the General-Purpose FPGA. Value of pin is copied to general-purpose register XXXXXXXXX. Can be used for user programs. This pin has no effect if FPGA ENABLE is logic 0.                                                                                                                                                                                                                                                                                                                                                                  |

| 3   | FPGA<br>ENABLE        | Input-Only Pin to the General-Purpose FPGA (U3). When this pin is logic 1 (SW3.3 is OFF), the FPGA is enabled and will transfer data from the DS3170 and FPGA as directed from the on-board microcontroller. When this pin is logic 0 (SW3.3 is ON), the FPGA is disabled. All inputs and outputs to the DS3170 and port FPGA are tri-stated. <b>Note:</b> This pin does not cause a hardware enable for the PORT FGPA.                                                                                                                                             |

| 4   | DATA<br>BUS<br>SELECT | Input-Only Pin to the General-Purpose FPGA (U3). When this pin is logic 1 (SW3.4 is OFF), the DS3170 and the port FPGA are set up such that they use the 16-bit bus from the on-board microcontroller. When this pin is logic 0 (SW3.4 is ON), the DS3170 and the port FPGA are set up such that they use the 8-bit bus from the on-board microcontroller. This pin has no effect if FPGA ENABLE is logic 0.                                                                                                                                                        |

| 5   | BOOT<br>SEL           | Input-Only Pin to the On-Board Microcontroller. When this pin is logic 1 (SW3.5 is OFF), the on-board microcontroller loads the firmware from an external source rather than the internal flash bank. When this pin is logic 0 (SW3.5 is ON), the microcontroller loads the firmware from the internal flash bank. If you choose to load code from an external source, refer to the user manual for the on-board microcontroller (U2) to ensure that all the timing and data are correct to run this program. This option should only be used by the advanced user. |

| 6   | KIT                   | Input-Only Pin to the On-Board Microcontroller. Not implemented with the firmware shipped from Dallas Semiconductor. This pin can be used by a user program.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7   | USER<br>INPUT 1       | Input/Output Pin to the General-Purpose FPGA (U3). This pin has an LED (DS4) to track the value of this signal. This pin has no effect if FPGA ENABLE is logic 0. <b>Note:</b> If you choose to use this as an output, USER INPUT 1 (SW3.7) must be in the off position.                                                                                                                                                                                                                                                                                            |

| 8   | USER<br>INPUT 2       | Input/Output Pin to the General-Purpose FPGA (U3). This pin has an LED (DS5) to track the value of this signal. This pin has no effect if FPGA ENABLE is logic 0. <b>Note:</b> If you choose to use this as an output, USER INPUT 1 (SW3.8) must be in the off position.                                                                                                                                                                                                                                                                                            |

#### SOFTWARE CONFIGURATION

## Quick Start (Software—ChipView)

- Perform steps in the Quick Start (Hardware Settings).

- Load ChipView software.

- Select COM port.

- Select Register View.

- From the Programs menu, launch the host application named ChipView.EXE. If the default installation options were used, click the Start button on the Windows toolbar and select Programs → ChipView → ChipView.

- Load the DS3170DK.DEF file.

- Make sure that all the register settings are correct for the proper function desired for the DS3170DK.

- Refer to the DS3170 data sheet for all questions pertaining to device functionality.

## **MEMORY MAP**

The on-board microcontroller is configured to start the user address space at 0x81000000. All offsets given in <a href="Table 7">Table 7</a> are relative to the beginning of the user address space. All device registers can be easily modified using ChipView.EXE host-based user-interface software.

**Table 7. Relative Address Map**

| REF DES | DEVICE                                    | OFFSET |

|---------|-------------------------------------------|--------|

| U3      | General-purpose FPGA                      | 0x0000 |

| U6      | FPGA Tx/Rx clock, data switch/mux         | 0x1000 |

| U7      | DS3170 DS3/E3 single-<br>chip transceiver | 0x2000 |

Table 8. General-Purpose Memory Map

| OFFSET | REGISTER NAME | TYPE      | DESCRIPTION                      |

|--------|---------------|-----------|----------------------------------|

| 0x00   | BRDID         | Read Only | Board ID                         |

| 0x02   | DSIDH         | Read Only | Dallas Extended ID Upper Nibble  |

| 0x03   | DSIDM         | Read Only | Dallas Extended ID Middle Nibble |

| 0x04   | DSIDL         | Read Only | Dallas Extended ID Lower Nibble  |

| 0x05   | BRDREV        | Read Only | Board Rev                        |

| 0x06   | ASMREV        | Read Only | Assembly Rev                     |

| 0x07   | FPGAREV       | Read Only | FPGA Firmware Rev                |

| 80x0   | CTRL1         | Control   | Control Reg #1                   |

#### ID REGISTERS

BID: BOARD ID (Offset=0X0000)

BID is read only with a value of 0xD.

XBIDH: HIGH NIBBLE EXTENDED BOARD ID (Offset=0X0002)

XBIDH is read only with a value of 0x00.

XBIDM: MIDDLE NIBBLE EXTENDED BOARD ID (Offset=0X0003)

XBIDM is read only with a value of 0x07.

XBIDL: LOW NIBBLE EXTENDED BOARD ID (Offset=0X0004)

XBIDL is read only with a value of 0x00.

BREV: BOARD FAB REVISION (Offset=0X0005)

BREV is read only and displays the current fab revision.

AREV: BOARD ASSEMBLY REVISION (Offset=0X0006)

AREV is read only and displays the current assembly revision.

PREV: PLD REVISION (Offset=0X0007)

PREV is read only and displays the current PLD firmware revision.

## **CONTROL REGISTERS**

Register Name: CTRL1

Register Description: Control Register 1

Register Offset: 0x0008

Bit# 7 6 5 4 3 2 1 0 SPI CPOL SPI CPHA SPI SWAP SPI HIZ WIDTH MOT MUX Name Default 0 0 0 0 0 1 0 0

Bit 7: SPI CPOL: This bit controls the SPI Interface Clock Polarity pin, which is muxed with the D7 pin on the

DS3170. Bit 7 is only active when bit 4 (SPI) is a logic 1. Refer to the DS3170 data sheet

for pin operation.

Bit 6: SPI\_CPHA: This bit controls the SPI Interface Clock Phase pin, which is muxed with the D6 pin on the

DS3170. Bit 6 is only active when Bit 4 (SPI) is a logic 1. Refer to the DS3170 data sheet

for pin operation.

Bit 5: SPI\_SWAP: This bit controls the SPI Interface Bit Order Swap pin, which is muxed with the D5 pin on

the DS3170. Bit 5 is only active when Bit 4 (SPI) is a logic 1. Refer to the DS3170 data

sheet for pin operation.

Bit 4: SPI: This bit controls the SPI Bus Mode bit.

0 = parallel bus mode 1 = SPI bus mode

Bit 3: HIZ: This bit controls the high-impedance test-enable bit (active low). This signal puts all the

digial outputs and bidirectional outputs to a high-impedance state when pulled low and

also when the JTRST is pulled low. For nomal operation, keep it as a logic 1.

**Bit 2: WIDTH:** This bit controls the databus width pin for parallel bus mode.

0 = 8-bit parallel mode 1 = 16-bit parallel mode

**Bit 1: MOT:** This bit controls the MODE pin for the DS3170.

0 = RD/WR strobe mode (Intel) 1 = DS strobe mode (Motorola)

Bit 0: MUX: This bit determines if the ALE pin on the DS3170 is in mux mode or nonmux mode

(constantly high). 0 = nonmux mode 1 = mux mode

Register Description: Control Register 2-Line IO

Register Offset: 0x0009

Bit# 7 6 5 4 3 2 1 0 RNEG2 RPOS3 RPOS1 RNEG3 RNEG1 RNEG0 RPOS2 RPOS0 Name Default 0 0 0 0 0 0 0

Bits 7 to 4: RNEGx: These bits control the source of the RNEG signal.

Bits 3 to 0: RPOSx: These bits control the source of the RPOS signal.

| RPOSx     | DESCRIPTION |

|-----------|-------------|

| 0x00      | HI-Z        |

| 0x01      | TPOS        |

| 0x02      | T3 OSC      |

| 0x03      | E3 OSC      |

| 0x04      | STS1 OSC    |

| 0x05      | BNC_INPUT   |

| 0x06      | Logic 0     |

| 0x07      | Logic 1     |

| 0x08-0xFF | HI-Z        |

| RNEGx     | DESCRIPTION |

|-----------|-------------|

| 0X00      | HI-Z        |

| 0X01      | TNEG        |

| 0X02      | T3 OSC      |

| 0X03      | E3 OSC      |

| 0X04      | STS1 OSC    |

| 0X05      | BNC_INPUT   |

| 0X06      | Logic 0     |

| 0X07      | Logic 1     |

| 0X08-0XFF | HI-Z        |

Register Name: CTRL3

Register Description: Control Register 3–Line RCLK

Register Offset: 0x000A

| Bit #   | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |

|---------|---|---|---|---|--------|--------|--------|--------|

| Name    | _ | _ | _ | _ | RLCLK3 | RLCLK2 | RLCLK1 | RLCLK0 |

| Default | 0 | 0 | 0 | 0 | 0      | 0      | 0      | 0      |

Bits 7 to 4: These bits are unused.

Bits 3 to 0: RLCLKx: These bits control the source of the RLCLK signal.

| RLCLKx    | DESCRIPTION |

|-----------|-------------|

| 0X00      | HI-Z        |

| 0X01      | TLCLK       |

| 0X02      | T3 OSC      |

| 0X03      | E3 OSC      |

| 0X04      | STS1 OSC    |

| 0X05      | BNC_INPUT   |

| 0X06      | Logic 0     |

| 0X07      | Logic 1     |

| 0X08-0XFF | HI-Z        |

Register Description: Control Register 4 Overhead Interface

Register Offset: 0x000B

| Bit #   | 7      | 6      | 5      | 4      | 3    | 2    | 1    | 0    |

|---------|--------|--------|--------|--------|------|------|------|------|

| Name    | TOHEN3 | TOHEN2 | TOHEN1 | TOHEN0 | TOH3 | TOH2 | TOH1 | TOH0 |

| Default | 0      | 0      | 0      | 0      | 0    | 0    | 0    | 0    |

Bits 7 to 4: TOHENx: These bits control the source of the TOHEN signal.

Bits 3 to 0: TOHx: These bits control the source of the TOH signal.

| TOHENx    | DESCRIPTION |

|-----------|-------------|

| 0X00      | HI-Z        |

| 0X01      | TOHSOF      |

| 0X02      | ROHSOF      |

| 0X03      | Not used    |

| 0X04      | Not used    |

| 0X05      | Not used    |

| 0X06      | Logic 0     |

| 0X07      | Logic 1     |

| 0X08-0XFF | HI-Z        |

| TOHx      | DESCRIPTION |

|-----------|-------------|

| 0X00      | HI-Z        |

| 0X01      | ROH         |

| 0X02      | Not used    |

| 0X03      | Not used    |

| 0X04      | Not used    |

| 0X05      | Not used    |

| 0X06      | Logic 0     |

| 0X07      | Logic 1     |

| 0X08-0XFF | HI-Z        |

Register Description: Control Register 5 Serial Data Overhead Interface

Register Offset: 0x000C

| Bit #   | 7 | 6 | 5 | 4 | 3     | 2     | 1     | 0     |

|---------|---|---|---|---|-------|-------|-------|-------|

| Name    | _ | _ | _ | _ | TSER3 | TSER2 | TSER1 | TSER0 |

| Default | 0 | 0 | 0 | 0 | 0     | 0     | 0     | 0     |

Bits 7 to 4: These bits are unused.

Bits 3 to 0: TSERx: These bits control the source of the TSER signal.

| TSERx     | DESCRIPTION |

|-----------|-------------|

| 0X00      | HI-Z        |

| 0X01      | RSER        |

| 0X02      | Not Used    |

| 0X03      | Not Used    |

| 0X04      | Not Used    |

| 0X05      | Not Used    |

| 0X06      | Logic 0     |

| 0X07      | Logic 1     |

| 0X08-0XFF | HI-Z        |

Register Description: Control Register 6 Serial Data Overhead Interface

Register Offset: 0x000D

Bit # Name Default

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TSOFI3 | TSOFI2 | TSOFI1 | TSOFI0 | TCLKI3 | TCLKI2 | TCLKI1 | TCLKI0 |

| 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Bits 7 to 4: TSOFIx: These bits control the source of the TSOFI signal.

Bits 3 to 0: TCLKIx: These bits control the source of the TCLKI signal.

| TSOFIx    | DESCRIPTION |

|-----------|-------------|

| 0X00      | HI-Z        |

| 0X01      | TSOFO       |

| 0X02      | RSOFO       |

| 0X03      | Not Used    |

| 0X04      | Not Used    |

| 0X05      | Not Used    |

| 0X06      | Logic 0     |

| 0X07      | Logic 1     |

| 0X08-0XFF | HI-Z        |

| TCLKIx    | DESCRIPTION |

|-----------|-------------|

| 0X00      | HI-Z        |

| 0X01      | TCLKO       |

| 0X02      | RCLKO       |

| 0X03      | Not Used    |

| 0X04      | Not Used    |

| 0X05      | Not Used    |

| 0X06      | Logic 0     |

| 0X07      | Logic 1     |

| 0X08-0XFF | HI-Z        |

### **DS3170 INFORMATION**

For more information about the DS3170, refer to the DS3170 data sheet available on our website at <a href="www.maxim-ic.com/DS3170">www.maxim-ic.com/DS3170</a>. Software downloads are also available for this design kit.

#### **DS3170DK INFORMATION**

For more information about the DS3170DK including software downloads, consult the DS3170DK data sheet available on our website at <a href="https://www.maxim-ic.com/DS3170DK">www.maxim-ic.com/DS3170DK</a>.

## **TECHNICAL SUPPORT**

For additional technical support, e-mail your questions to <a href="telecom.support@dalsemi.com">telecom.support@dalsemi.com</a>.

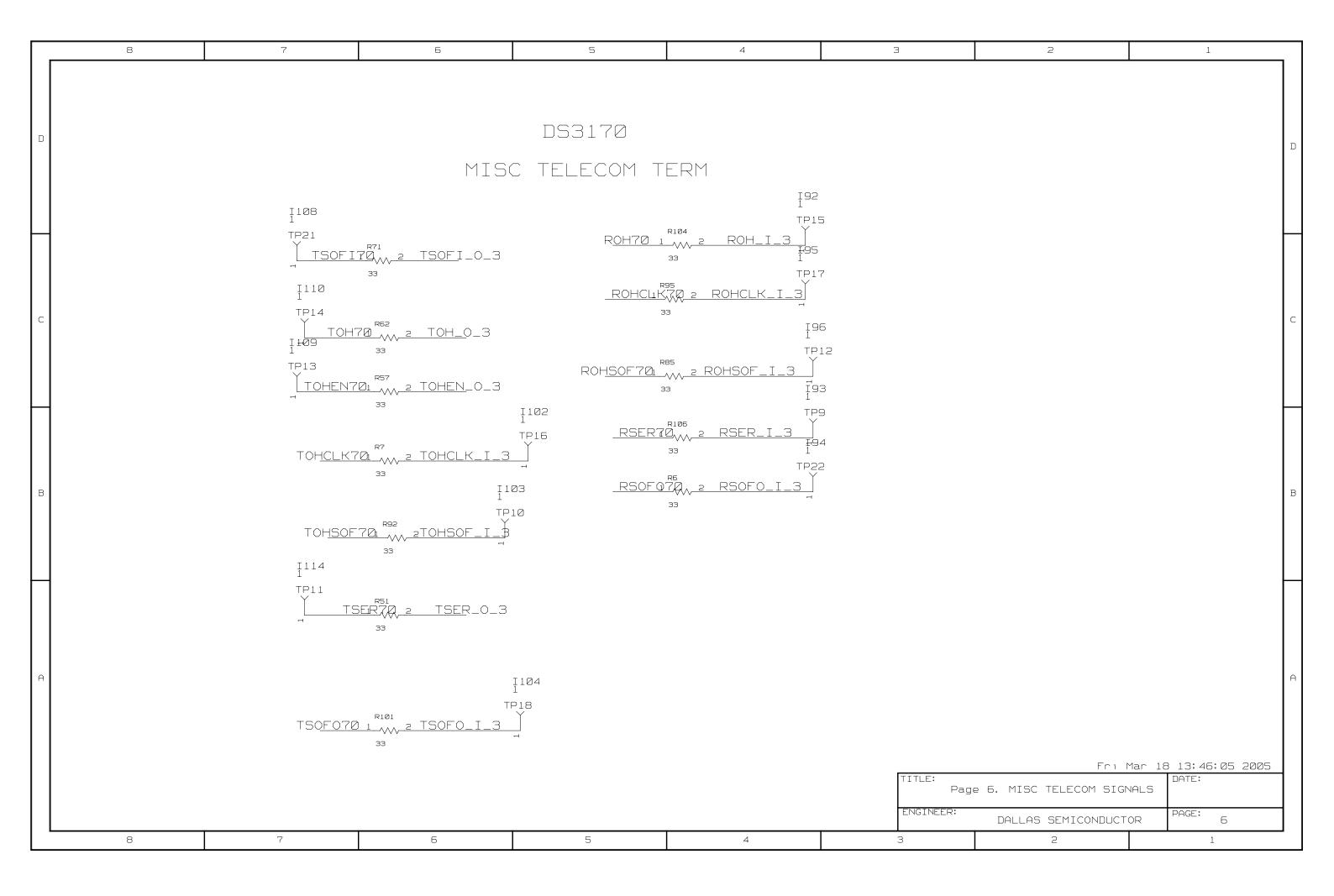

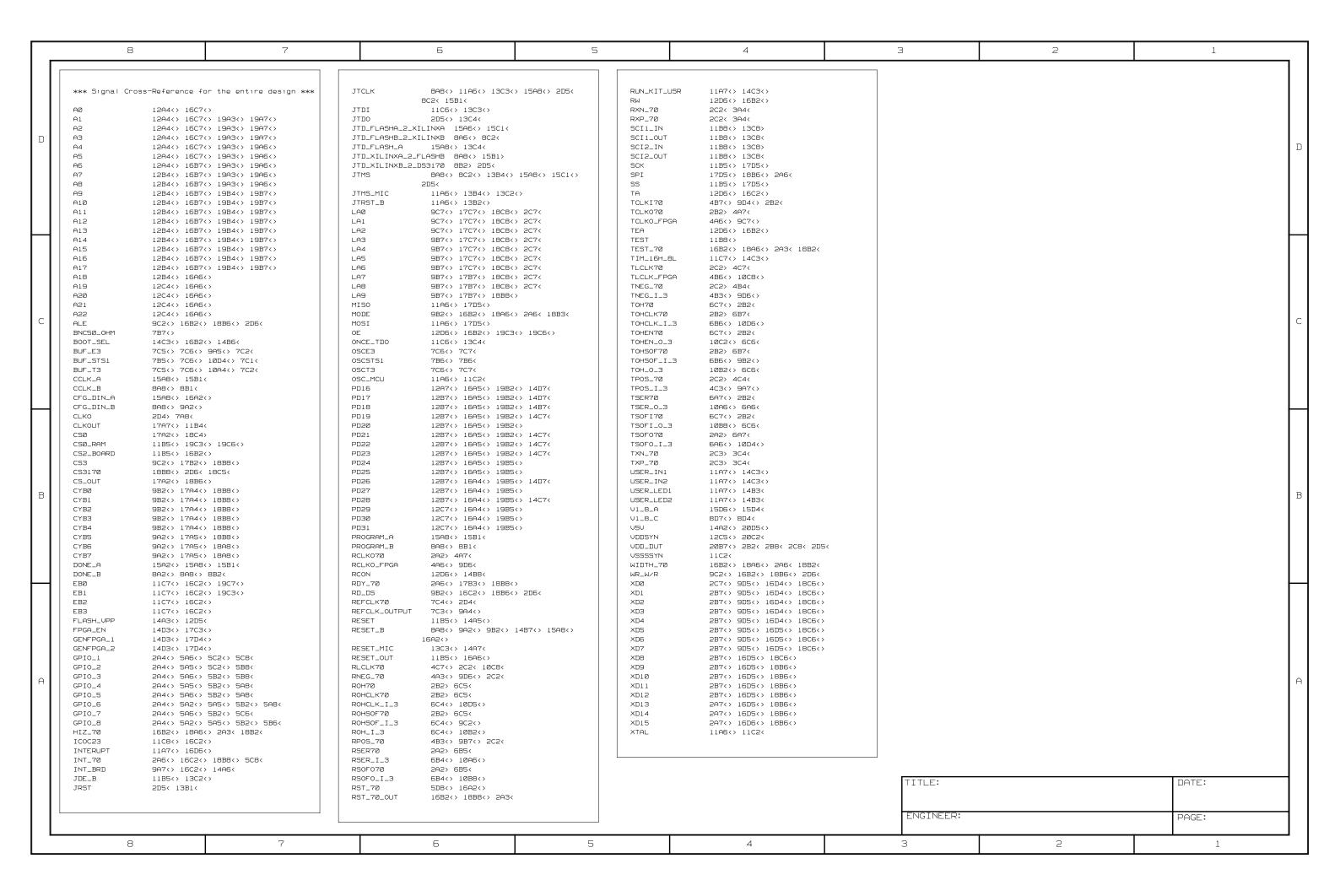

### **SCHEMATICS**

The DS3170DK schematics are featured in the following 23 pages.

|   | 8 7                               | Б            | 5                                | 4                               | 3                               | 2                 | 1               |      |  |

|---|-----------------------------------|--------------|----------------------------------|---------------------------------|---------------------------------|-------------------|-----------------|------|--|

|   |                                   |              |                                  |                                 |                                 |                   |                 |      |  |

| D |                                   | DS31'        | 70 DES                           | STGN K                          |                                 |                   |                 | D    |  |

|   |                                   |              | CREATED                          |                                 | · <del></del>                   |                   |                 |      |  |

|   |                                   |              | S SEMIC                          |                                 | )R                              |                   |                 |      |  |

| П |                                   |              | JNE 26,                          |                                 |                                 |                   |                 |      |  |

|   |                                   |              |                                  |                                 |                                 |                   |                 |      |  |

| С | Page 1. COVER PAGE                |              |                                  |                                 | Page 11. MICROCONTROLLER BLOCK1 |                   |                 |      |  |

|   | Page 2. DS3170                    | ð BGA        | Page 1                           | Page 12. MICROCONTROLLER BLOCK2 |                                 |                   |                 |      |  |

| Ц | Page 3. LIU INTERFACE             |              |                                  |                                 | Page 13. SERIAL/JTAG CONN       |                   |                 |      |  |

|   | Page 4. TCLK/F                    | RCLK/TELECOI | M DATA                           | Page 1                          | 4. MISC US                      | ER INPUTS         |                 |      |  |

|   | Page 5. DS3170                    | Page 1       | Page 15. GP FPGA CONTROL / FLASH |                                 |                                 |                   |                 |      |  |

| В | Page 6. MISC 1                    | Page 1       | Page 16. GP FPGA BLOCK1          |                                 |                                 |                   |                 |      |  |

|   | Page 7. REF OSC                   |              |                                  |                                 | Page 17. GP FPGA BLOCK2         |                   |                 |      |  |

| H | Page 8. PORT FPGA CONTROL / FLASH |              |                                  | Page 1                          | Page 18. ADDRESS/DATA HEADERS   |                   |                 |      |  |

|   | Page 9. PORT FPGA BLOCK1          |              |                                  |                                 | Page 19. MICROCONTROLOR SRAM    |                   |                 |      |  |

|   | Page 10. PORT FPGA BLOCK2         |              |                                  | Page 2                          | Page 20. POWER CONN             |                   |                 |      |  |

| A |                                   |              |                                  | Page 2                          | Page 21. NOTES                  |                   |                 |      |  |

|   |                                   |              |                                  | _                               |                                 |                   |                 |      |  |

|   |                                   |              |                                  |                                 | TITLE:                          |                   | Mar 18 13:45:59 | 2005 |  |

|   |                                   |              |                                  |                                 | ENGINEER:                       | age 1. COVER PAGE | PAGE: 1         |      |  |

|   | 8 7                               | 6            | 5                                | 4                               | 3                               | DALLAS SEMICONDUC | 1               |      |  |

|   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                                                                                                                                                                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                       | 4                                                                                                                                                                                         | 3                                                                                                                                                                                                                                                                                           | 2                                                                                                                                                               | 1     | $\overline{}$ |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------|

| ם | *** Part Cross-Reference for '  C1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D D D D D D D D D D D D D D D D D D D                                                                                                                                                                    | 12 DIODE 2085 151 LED 14C2 152 LED 15A1 153 LED 14A3 154 LED 14B2 155 LED 14B2 156 LED 8A1 157 LED 18B4 158 LED 18B5 159 LED 18B5 1510 LED 18B5 1511 LED 5C7 1512 LED 5B7                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R32 RE: R33 RE: R34 RE: R35 RE: R36 RE: R37 RE: R39 RE: R40 RE: R41 RE: R42 RE: R43 RE: R44 RE: R44 RE: R45 RE: R45 RE:                                                                                                                                                                                                                                                 | 51 14D3<br>51 14B6<br>51 14D3<br>51 14D3<br>51 14D4<br>51 14B2<br>51 14D4<br>51 14A6<br>51 14D4<br>51 4B7<br>51 4A7<br>51 14B6<br>51 14B5<br>51 14B5                                      | T1 TRANSFORI T2 TRANSFORI TP1 TESTPOIN' TP2 TESTPOIN' TP3 TESTPOIN' TP4 TESTPOIN' TP5 TESTPOIN'                                                                                                                                                                                             | DN 14B8 POS 14D2 POS 5C1 DN 5A4 PDT_SLIDE_6P 14A2 MER_PULSE 3A5 MER_PULSE 3C5 F1 20D4 F1 4C3 F1 4A6 F1 4A6                                                      |       |               |

| С | C14 CAP1 11A4 C15 CAP1 11A5 C16 CAP1 2C8 C17 CAP1 20C2 C18 CAP1 20A4 C19 CAP1 20A3 C20 CAP1 15D6 C21 CAP1 20A4 C22 CAP1 20A6 C23 CAP1 15D7 C24 CAP1 11A5 C25 CAP1 20B4 C26 CAP1 15A6 C27 CAP1 15A6 C27 CAP1 15A6 C28 CAP1 15A6 C29 CAP1 15A6 C30 CAP1 20A3 C31 CAP1 20A4 C32 CAP1 15A7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7:<br>2:<br>3:<br>4:<br>4:<br>4:<br>4:<br>4:<br>5:<br>5:<br>5:<br>5:<br>5:<br>6:<br>7:<br>7:<br>7:<br>7:<br>7:<br>7:<br>7:<br>8:<br>8:<br>8:<br>8:<br>8:<br>8:<br>8:<br>8:<br>8:<br>8:<br>8:<br>8:<br>8: | 4_40_HDWR_U 20D3 4_40_HDWR_U 20C3 4_40_HDWR_U 20C2 1 CONN_BANANA_2P 20B8 2 CONN_BBP 13B6 3 CONN_50P2 18D7 4 CONN_4_PIN 13C4 5 CONN_BNC_5P 7B7 6 CONN_10P 7D6 7 CONN_10P 5A5                                                                                                                                                                                                                                                                                                                                                                                                                                                | R47 RE: R48 RE: R49 RE: R50 RE: R51 RE: R52 RE: R53 RE: R55 RE: R55 RE: R56 RE: R57 RE: R58 RE: R60 RE: R61 RE: R62 RE: R63 RE: R63 RE: R64 RE: R65 RE:                                                                                                                                                                                                                 | 51 2A7<br>51 13C3<br>51 13B3<br>51 5A6<br>51 16C1<br>51 13B4<br>51 7C1<br>51 7C2<br>51 7C1<br>51 5C6<br>51 13C1<br>51 5C2<br>51 18B4<br>51 18B4<br>51 18B4<br>51 6C6<br>51 18B4<br>51 6C6 | TP6                                                                                                                                                                                                                                                                                         | T1 4C3 T1 4A3 T1 6B4 T1 6B6 T1 6C7 T1 6C7 T1 6C7 T1 6B5 T1 6B4 T1 6B6 T1 6B7 T1 6B8                                   |       | С             |

| В | C33 CAP1 15D6 C34 CAP1 15D6 C35 CAP 20D4 C36 CAP1 20D5 C37 CAP1 20D5 C38 CAP1 7B2 C39 CAP1 20B3 C40 CAP1 8C8 C41 CAP1 8D6 C42 CAP1 8D6 C43 CAP1 8B8 C44 CAP1 8B8 C45 CAP1 8B8 C46 CAP1 8B7 C47 CAP1 8B7 C47 CAP1 8B7 C48 CAP1 8B7 C48 CAP1 8D7 C49 CAP1 8D6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | JI<br>JI<br>JI<br>JI<br>JI<br>JI<br>L<br>PP<br>R<br>R<br>R<br>R<br>R<br>R<br>R                                                                                                                           | WR_CONNBAN1 CONN_BANANA_2P 20D8  WR_CONNBAN2 CONN_BANANA_2P 20C8  11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R66 RE: R67 RE: R68 RE: R69 RE: R70 RE: R71 RE: R72 RE: R73 RE: R74 RE: R75 RE: R76 RE: R77 RE: R78 RE: R78 RE: R78 RE: R79 RE: R79 RE: R80 RE: R81 RE: R82 RE:                                                                                                                                                                                                         | 51 13C1 51 4C6 51 7C1 51 7C1 51 5C7 51 4C7 51 4C7 51 5B2 51 5B7                                                     | U3 XC2SE_FT2 U4 CY62128V U5 MAX1792 U6 XC2SE_FT3 U7 D53170_B0 U8 MAX3233E U9 NC75Z86_L0 U10 X1LINX_X0 U11 CY62128V U12 XILINX_X0 U13 74_00 U14 NC75Z86_L0 U15 74_04 U16 NC75Z86_L0 U17 NC75Z86_L0 U17 NC75Z86_L0 U17 NC75Z86_L0 U18 NC75Z86_L0 U18 NC75Z86_L0 U18 NC75Z86_L0 U18 NC75Z86_L0 | 11C7 12C6 256_U 15C4 16C5 17B5 19B7 8D8 256_U 8C4 9B5 10C5 5A_U 2C5 13C7 U 15A2 CF015 15B7 19B4 CF015 8A7 14A6 14A7 14A8 U 8A2 18A4 18B3 18C3 U 7C5 U 7C5 U 7C5 |       | В             |

| А | C51 CAP1 2B8 C52 CAP1 7B5 C53 CAP1 7B5 C54 CAP1 7B3 C55 CAP1 7B3 C55 CAP1 7B3 C56 CAP1 7B4 C57 CAP1 20C4 C58 CAP1 20B3 C59 CAP1 7B3 C60 CAP1 7B4 C62 CAP1 7B4 C62 CAP1 2B8 C63 CAP1 2C7 C64 CAP1 2B1 C65 CAP1 2B1 C65 CAP1 2B8 C66 CAP1 2B1 C66 CAP1 2B8 C67 CAP1 3B5 C69 CAP1 3B5 C72 CAP1 3A5 C71 CAP1 3B5 C72 CAP1 7A2 C74 CAP1 7A2 C74 CAP1 7A2 C74 CAP1 7A2 C75 CAP1 7A2 C74 CAP1 7A2 C74 CAP1 7A2 C75 CAP1 7A2 C75 CAP1 7A2 C75 CAP1 7A2 C76 CAP1 7A2 C77 CAP1 7A3 C77 |                                                                                                                                                                                                          | 88     RES1     4A7       89     RES1     3A4       810     RES1     3C4       811     RES1     3C4       812     RES1     3C4       813     RES1     11C2       814     RES1     14C6       815     RES1     14C2       816     RES1     14C2       817     RES1     14D6       818     RES1     14C5       820     RES1     14C6       821     RES1     14D6       822     RES1     14D6       823     RES1     14D6       824     RES1     14D6       825     RES1     14B6       827     RES1     14C6       828     RES1     14C6       829     RES1     14C6       829     RES1     14A5       830     RES1     14A3 | R84 RE: R85 RE: R86 RE: R87 RE: R88 RE: R89 RE: R90 RE: R91 RE: R92 RE: R93 RE: R94 RE: R95 RE: R96 RE: R96 RE: R97 RE: R98 RE: R98 RE: R99 RE: R100 RE: R101 RE: R102 RE: R103 RE: R104 RE: R105 RE: R106 RE: R106 RE: R107 RE: R106 RE: R107 RE: R108 RE: R108 RE: R109 RE: R100 RE: R100 RE: R101 RE: R102 RE: R104 RE: R105 RE: R106 RE: R107 RE: R106 RE: R107 RE: | 51                                                                                                                                                                                        | U19 NC75Z86_L U20 NC75Z86_L U21 74_04 U22 MAK6B16 U23 NC75Z86_L U24 74_04 X1 XTAL Y1 05C2 Y2 05C2 Y3 05C2                                                                                                                                                                                   | J 7C3<br>5A7 5B8 5D2 5D3<br>5A3                                                                                                                                 | DATE: | А             |

|   | C75 CAP1 2B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                          | 31 RES1 14D3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R108 RE                                                                                                                                                                                                                                                                                                                                                                 | i                                                                                                                                                                                         | ENGINEER:                                                                                                                                                                                                                                                                                   |                                                                                                                                                                 | PAGE: |               |

|   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                                                                                                                                                                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5                                                                                                                                                                                                                                                                                                                                                                       | 4                                                                                                                                                                                         | 3                                                                                                                                                                                                                                                                                           | 2                                                                                                                                                               | 1     |               |